视频图像灰度信号直方图均衡的FPGA实现

直方图均衡作为一种基础的图像处理方法在很多领域得到应用,但大多是通过DSP或者CPU编程实现,其优点是灵活性比较高,调试方便,最大的缺点是很难做到实时或者准实时处理,这在某些领域是不可接受的。而使用FPGA实现可以很好地解决实时处理的难题,而且目前的FPGA资源容量已经很丰富,片内的SRAM/PLL/逻辑资源已经足以应对一般图像处理算法的需要,同时随着价格的不断下降,客观上使得FPGA成为图像处理算法实现不错的选择。

本文引用地址:http://www.amcfsurvey.com/article/191407.htm本文主要介绍在FPGA上实现直方图均衡算法的总体结构和最重要的两个子模块的实现细节,以及最终的实现结果。

1 直方图均衡的理论基础

原始图像灰度值r归一化在0~1之间,p(r)为原始图像灰度分布的概率密度函数。直方图均衡化处理实际上就是寻找一个灰度变换函数T,使得变化后的灰度值s=T(r), 其中,s归一化为0~1,即建立r与s之间的映射关系,要求处理后图像灰度分布的概率密度函数p(s)=1,期望所有灰度级出现概率相同。

对于数字图像离散情况,其直方图均衡化处理的计算步骤如下:

(1)统计原始图像的直方图

![]()

式中,rk是归一化的输入图像灰度;nk是输入图像中归一化灰度等于rk的像素个数;n是输入图像的像素总数。

(2)计算直方图累积分布曲线

![]()

(3)用累积分布函数作变换函数进行图像灰度变换

根据计算得到的累积分布函数,建立输入图像与输出图像灰度之间的对应关系,最后要将变换后的灰度恢复成原先范围。

2 FPGA实现的总体结构

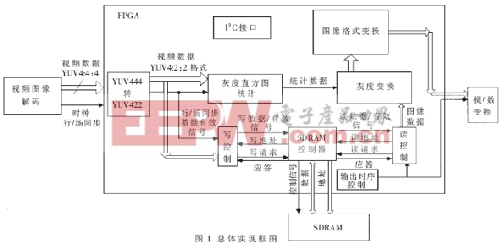

从上面对直方图均衡算法的描述可知,在进行直方图均衡以前,首先必须对图像灰度进行统计,然后再计算输出。而要统计一幅图像的全局灰度信息,就不得不把整幅图像先写入缓存。虽然FPGA内部的SRAM资源丰富,但是仍然无法满足整幅图像存储的需要。因此,需要以SDRAM作为图像缓存,存储前后两场视频图像,然后再计算输出。SDRAM的容量、速度都能满足直方图均衡算法的要求,唯一的缺点是必须有相应的SDRAM控制器控制SDRAM的读写和刷新操作。下面简要介绍总体实现的方案,其实现框图如图1所示。

从图1中可以看出,在输入端,模拟复合视频数据经过视频图像解码进入FPGA,在FPGA里先对数据进行简单处理,产生内部使用的行同步信号/场同步信号/数据有效信号和16bit YUV4:2:2格式的视频信号。然后,灰度信息进入灰度直方图统计模块对当前灰度信息出现的频率加以统计,将统计信息以乒乓的方式存入SRAM,与此同时所有视频数据通过“写”控制模块和SDRAM控制器存入SDRAM;在输出端,在“读”控制单元的控制下通过SDRAM控制模块从SDRAM读出上一场的数据进入灰度变换模块,根据存储的上一场的灰度统计信息,对数据进行灰度变换。这样就完成了完整的灰度直方图均衡变换。

如果需要在显示设备(如PC显示器)上显示,还必须要有时序产生/图像数据格式变换等模块。另外,由于需要对某些内部参数进行调整(如SDRAM的Latency等),必须有一个控制接口和外部相连,在这里使用了一个I2C协议接口。

在所有模块中最主要的实现单元主要有两大部分,一个是直方图统计和灰度变换模块,另一个是SDRAM控制器和读写控制单元。下面将详细介绍这两部分。

3 直方图统计的实现结构

直方图统计是通过FPGA内部两块双端口SRAM的乒乓操作实现的。其中每块SRAM的地址反映了灰度值的大小,而SRAM每个单元的数据宽度必须相应于每场图像的像素数量。例如,对于我国PAL制的电视图像来说,根据ITU-R BT.601/656数字视频标准规定每一场数字化后的视频图像,它的有效数据是每行720个有效点,每场288个有效行,每场总共207360个有效像素点,平均每个点16bit的数据量,其中有8bit灰度数据。所以在选取SRAM的大小时,应该选择容量为256(2的8次方)、数据宽度为18位(207 360大于2的17次方)的SRAM。但是为了扩展的方便,实际使用中使用了容量为256、数据宽度为22位的SRAM,这样可以对数据量更大的图像加以处理。

评论