应对FPGA/SDI子系统中的高速板布局挑战

简介

电视和影院已经进入数字时代。视频图像曾以标准传输率(270Mb/s)传输,后来升级到高传输率(1.485Gb/s),现在已上升到3Gb/s。更高传输率实现了更高分辨率的娱乐图像传输,但同时也使硬件工程师和物理布局设计师面临着更大的挑战。很多视频系统都采用多功能FPGA和多传输率SDI集成电路,以支持高性能专业视频在长距离的传输。FPGA需要高密度、细迹线宽度的传输,而高速模拟SDI传输需要阻抗匹配和信号保真。本论文概述了硬件工程师面临的挑战,并为处理这些挑战提供了建议。

FPGA/SDI子系统

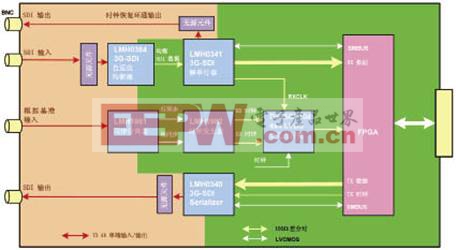

在典型的FPGA/SDI板中,数字视频信号在BNC(卡拴式同轴接头)与高性能SDI75迹线模拟集成电路之间传输。FPGA和SDI集成电路之间的互连包含通过FPGA细间距球栅发送的多对100差分信号。其中一个布局难点是75单端迹线和100差分迹线的共存。通常,这两种迹线在元件所在顶层上传输。适合75的迹线宽度对于100迹线可能过宽。图1是FPGA/SDI的示意框图,显示75和100的两个区。

图1 典型FPGA/SDI框图

SDI布局难点

电影与电视工程师学会(SMPTE)发布了同轴电缆上数字视频的传输标准。规定信号幅值为800mV±10%。必须通过芯片外的75±1%精确终端电阻器满足此幅值要求。SMPTE标准还包含输入和输出的回波损耗要求,基本规定了输入或输出端口如何近似于75网络。图2显示SMPTE对回波损耗的要求。

芯片外阻抗平衡网络由电感器和并联电阻器构成,通常用于抵消SDI集成电路的输入或输出电容。大交流耦合电容器(4.7µF)通常用于传输SDI串行位流,以避免低频直流漂移。如图3所示,75迹线的SDI集成电路及其BNC连接器之间附有多个芯片外无源元件。每个元件都具有串联寄生电感,每个元件焊盘又具有并联寄生电容,从而影响与75匹配的总阻抗。SDI布局的难点在于最大限度减少外部无源元件在75SDI端口造成的阻抗失配。

选择FPGA/SDI子系统的板堆叠

应该使用什么迹线宽度 在小于3Gb/s的SDI速度中,铜损耗很小,并不构成选择迹线宽度的重要考虑因素。选择略小于元件接合焊盘的迹线宽度更为重要,以最大限度减少阻抗失配。0402尺寸的无源元件需要20密尔x25密尔的接合焊盘,以使15密尔到20密尔的迹线宽度最适合于75SDI迹线。

为了便于传输和偏斜匹配,FPGA的100差分信号使用细迹线宽度传输。宽松的耦合迹线通常用于避免较大的阻抗变化,而分支出的紧密耦合迹线则连接到终端电阻器或交流耦合电容器。

图4显示了适用于FPGA和SDI信号传输的板堆叠。在此堆叠中,SDI信号迹线采用在第4层以GND2为基准的75单端微带线。GND2是在第4信号层形成的金属岛。第2和第3层的金属(GND1和VCC面)在75迹线区被移除,以使其不会降低迹线的特征阻抗。FPGA的100差分迹线是在第2层以GND1为基准的宽松耦合微带线。两个接地基准(GND1和GND2)通过接地缝补镀通孔相连。此板堆叠排列允许通过调节绝缘长度h2自由选择75迹线的宽度,以及通过调节h1自由选择100迹线的宽度。

评论