基于FPGA的8085A CPU结构分析与实现

1 引 言

微型计算机原理几乎是所有理工科类大学生的必修课目之一, 其重要性不言而喻。然而大多数教学侧重于应用方面, 对计算机的结构及工作原理涉之不深, 因为无法做一个CPU 来演示。这样学生不能真正了解其性能特点, 掌握内部结构, 在学习汇编语言的时候增加了难度, 影响学习兴趣。随着可编程逻辑器件的广泛应用, 给数字系统的设计带来了极大的灵活性, 用户可以利用现场可编程门阵列FPGA 来开发出一个适合自己的专用CPU, 对微型计算机的原理及结构进行充分理解与研究, 便于将来从事相关ASIC设计, 开发出创新型的产品, 为我国计算机发展做贡献。

现场可编程门阵列FPGA 门数众多, 人们可以将合适的IP软核或其他形式的核作为嵌入式模块装在自己的设计中。但通常IP软核需要门数较多的FPGA 器件支持, 作为学习来说的FPGA 芯片往往资源有限, 需要节约FPGA 的成本与面积; 并且没必要实现所有功能, 只要做出关键部分及重要结构,明白其运行机理, 又能与真实的CPU 紧密相联即可。实验箱上采用的FPGA 芯片为A ltera 公司的EPF10K20TC144- 4。这里以Inte l的8085A 为例来说明8位计算机的工作原理。

2 8085A CPU 设计及实现

2. 1 FPGA 芯片及外围电路简介

A ltera的FLEX10K 器件是工业界首例嵌入式PLD, 基于可重配置CMOS SRAM 元件。EPF10K20带有144个LAB (逻辑阵列块) 和1152 个逻辑单元, 最大I/O数目为189。另外, 芯片中嵌入式陈列块( EAB)有6个, 其RAM 总位数为12288。

实验涉及到FPGA 芯片的外围部分包括控制开关、2* 8键盘输入、6个数码管输出、8个输入端口、8个输出端口及2个中断开关等。主要用来增添程序设计的灵活性及形象性, 使其可现场调试, 验证结果, 避免单纯用软件仿真的不足。外围电路控制模块及结构可参见文献[ 1] 。

现场调试时可以通过控制开关, 手动从键盘输入相应的地址及数据(通过数码管显示), 输错可以修改; 用写使能开关给RAM 写入相应程序。当输入完所有程序后, 按下运行开关即可执行程序, 在数码管上显示地址、数据及最终结果。控制开关用于配合键盘通过手动方式输入程序, 可以形象化的现场编程。在软件下载后不使用计算机, 通过按钮、键盘就能将程序输入到RAM 中, 然后运行, 显示出结果。

2. 2 CPU模块

2. 2. 1 内部结构

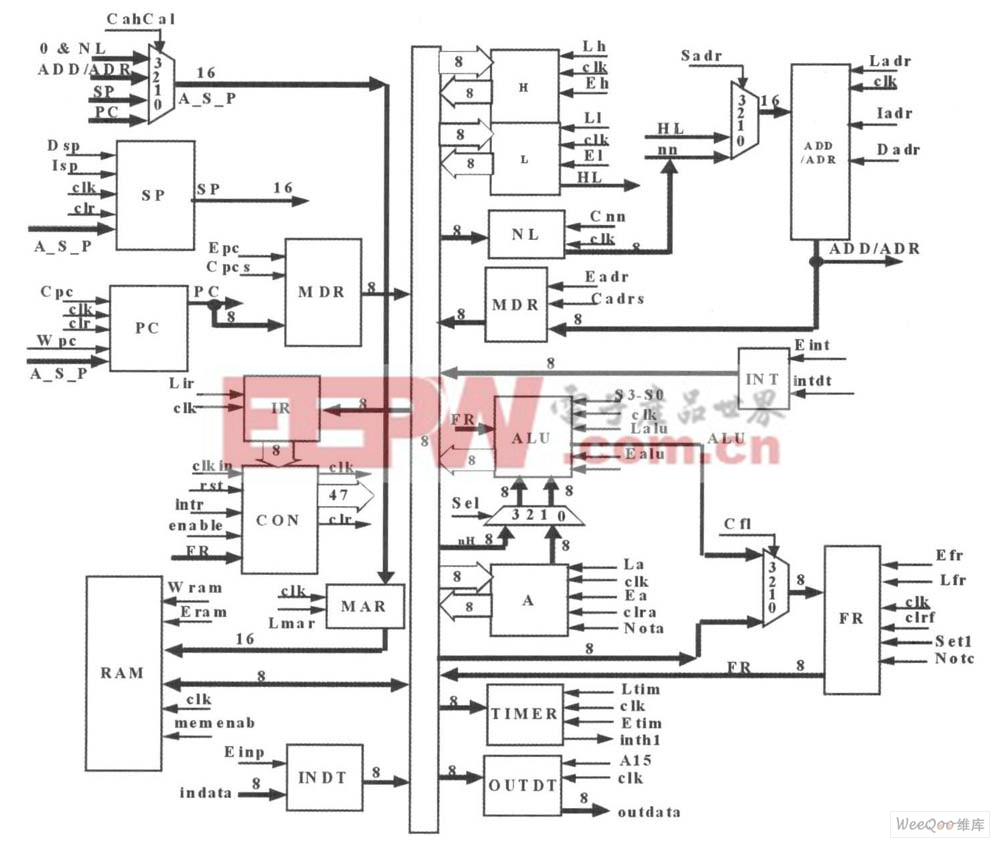

CPU 模块的内部结构如图1所示。微型计算机由下面几个部分组成: 8位通用寄存器H、L, 16位程序计数器( PC ) , 16位堆栈指示器( SP), 一个加1 /减1 地址锁存器( ADD /ADR ), 8 位NL 寄存器( NL) , 8位中断时间寄存器( T IMER ) ; 算术逻辑单元(ALU ), 累加器(A ), 标志寄存器( FR ), 数据选择器( SEL) ; 指令寄存器( IR) , 控制器( CON ) , 4选1多路选择器(MUX) , 存储地址寄存器(MAR ) , 8 位数据寄存器(MDR) ; 输入数据寄存器( INDT ), 输出数据寄存器( OUTDT )等部分组成。其中标志寄存器有4位, 分别是: 进位位( Cy)、零位( Z)、符号位( S)、奇偶位( P) , 微机通过检测这些标志位的1位或多位来判断程序是否需要转移。

微型计算机CPU 结构图

图1 微型计算机CPU 结构图

图中字母L为数据载入控制信号, E 为三态输出选通信号, clk为时钟信号, c lr为清零信号, W 为数据载入PC信号, Cpc为控制PC 加1信号, S3- S0为控制ALU 进行加减、逻辑运算或移位运算的选择信号, Iadr、Dadr为加1 /减1地址锁存器加1减1控制信号, Isp、Dsp为堆栈指示器的加1减1 控制信号, E ram、W ram 为读写RAM 控制信号。另外, 累加器(A ) , 标志寄存器( FR )增加了专用的清零信号。

所有的控制、时钟及清零信号由控制器( CON)模块给出, 而CON 模块由外部时钟clkin、清零信号rst及使能信号enable 控制。存储地址寄存器(MAR )用来给RAM输送地址, 从RAM 读指令和数据, 也可以给RAM写数据。

评论