基于FPGA的语音存储与回放系统设计

1 设计要求

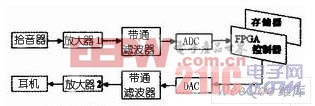

本文引用地址:http://www.amcfsurvey.com/article/191315.htm设计并制作一个数字化语音存储与回放系统,其示意图如图1所示。

(1)放大器1的增益为46dB,放大器2的增益为40dB,增益均可调;

(2)带通滤波器:通带为300Hz~3.4kHz;

(3)ADC:采样频率fs=8kHz,字长=8位;

(4)语音存储时间≥10s;

(5)DAC:变换频率fc=8kHz,字长=8位;

(6)回放语音质量良好。

不能使用单片语音专用芯片实现本系统。

2 数字化语音存储与回放系统硬件电路

2.1 放大器1即音频信号放大电路

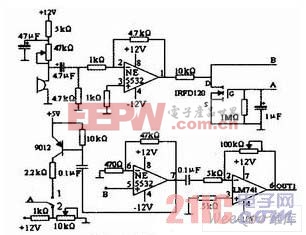

音频信号放大电路如图2所示。第一级放大(-4.7)倍。IRD120实现自动增益控制,当开关打到1的位置是增益自动控制,当开关打到2的位置是手动控制。增益自动、手动控制是利用场效应管工作在可变电阻区,漏源电阻受栅源电压控制的特性。第二级放大(+101)倍。第三级放大倍数可调,最大(-20)倍,保证ADC0809满量程转换。

图2 音频信号放大电路

2.2 带通滤波器

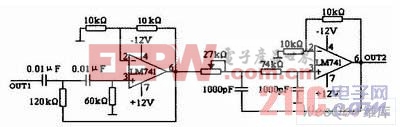

带通滤波器如图3所示。实测带通300~3300Hz。保证语音信号不失真地通过滤波器,滤除带外的低频信号和高次谐波。

图3 带通滤波器

评论