多路接口与E1协议转换器设计与实现

摘要:针对通信带宽越来越高,低速设备无法连接到高速的E1线路的问题,提出了一种基于可编程逻辑器件FPGA、嵌入式微处理器MPC875的多路接口与E1协议转换器的设计,给出了硬件原理框图及主要元器件的选型,并对多路接口数据调度方法、空时隙处理策略、FPGA结构设计、软件设计流程进行了详细说明。通过实现RS 232,RS 449,V.35三路接口与E1的协议转换,证明该方案是可行的。

关键词:多路接口;E1;协议转换;FPGA

0 引言

随着计算机技术与通信技术的持续发展,人们对高带宽需求不断增加,接入DDN(Digital Data Network)网、帧中继网等高速通信网的应用也越来越普遍。E1是我国电信传输网一次群使用的传输标准,速率是2.048 Mb/s。实现多路接口与E1协议的相互转换,将可以把多种设备同时连接至高速的E1线路。本文基于FPGA(Field Programmable Gate Array)、嵌入式微处理器设计了一个多路接口与E1的协议转换器,实现RS 232,RS 449,V.35等接口数据在E1线路上的高速传输。

1 系统原理

1.1 系统描述

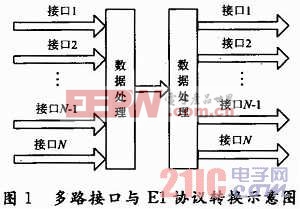

多路接口与E1协议转换示意图如图1所示。在发送端,将多路接口数据按照一定顺序合并成一路符合E1协议的数据在E1信道上进行传输,在接收端,将接收到的E1信号再按发送端顺序分成多路接口数据。

1.2 多路接口数据映射到E1帧的方法

E1是一种典型的时分复用结构,一个E1时分复用帧划分为32个相等的时隙,编号为CH0~CH31,其中时隙CH0用作帧同步用,时隙CH16用来传送信令。其余的时隙用来传送有效数据。

通过将不同的接口数据插入不同的数据时隙,把多路接口数据编成一个E1数据帧,实现多路接口与E1的协议转换。

将多路接口数据映射到E1时隙中,需要根据每路接口的速率进行时隙分配,也就是将E1的一个或多个时隙分配给一路接口使用,分配的时隙速率不小于接口速率(每个时隙的速率相当于64 Kb/s),DTE(Data Terminal Equipment)与DCE(Data Communications Equipment)设备端时隙分配设置必须一致。由于协议转换器没有自适应接口速率的功能,因此时隙的分配通过一个软件界面由使用者完成。

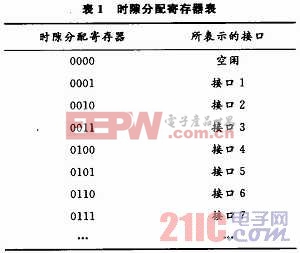

为了实现对时隙的分配,设置30个4位的时隙分配寄存器。CPU根据使用者的时隙分配设置,生成30个数据时隙地址并写入对应时隙分配寄存器。数据时隙地址表示的是该数据时隙传送的是哪个接口的数据。在发送端,根据该地址从相应接口读取数据插入对应时隙;在接收端,根据该地址将相应时隙数据送往对应接口。表1为数据时隙地址与接口对应关系表,空闲表示该时隙空置没有使用。

系统将E1时隙分配给多路接口使用,当有时隙没有被分配时,就会产生空时隙。在本设计中,系统可支配的最小单位是E1时隙,也就是说,系统可以将一个数据时隙分配给一路接口使用,也可以将多个数据时隙分配给一路接口使用,当一路接口数据不能完全填满一个或多个时隙时,将会产生半空时隙。比如一个100 Kb/s的接口,占用两个时隙,将会产生28 Kb/s的空时隙。

评论