基于扫描的电路设计

为了确保芯片在制作完成后的正确性,有关电路测试的这个问题越来越受重视。而且其测试的难度及成本也越来越高,于是如何有效地检验电路的正确性,并大幅度地降低测试成本,成为我们现在研究的热点。通常我们在设计芯片的同时,可以根据芯片本身的特征,额外地把可测性电路设计(Design For Testability)在芯片里。谈到可测性的电路设计,内建自测试(BIST)和基于扫描Scan—Based)的电路设计是常被提及的。

本文引用地址:http://www.amcfsurvey.com/article/191173.htm基于扫描的电路设计是可测性设计中最常用的一种方法。它是属于Test—Per—Scan测试方法的电路。

目前的测试方法有两种,一种是Test—Per—Scan,另一种是Test—Per—Clock,这两种测试方法各有各的优缺点。所谓Test—Per—Scan的运作方式,就是我们将一个电路里的全部或部分寄存器串联起来,形成一条扫描链,然后将测试序列在每个周期移入一个值,直到测试向量填满整个扫描路径为止,再经过一个周期后,我们将待测电路的测试结果传到扫描链里。最后移出做压缩分析。这种方法的优点是很容易运用在任何商业性的设计流程中,而且其硬件架构对系统功能的影响较小,控制硬件设计也较为简单:缺点是要*较多的时间来产生测试向量,测试速度慢。所谓Test—Per一Clock,就是当我们在测试电路的时候,每一个周期都送进一个新的测试向量进入电路,同时在电路的输出得到测试的结果,所以这种方式的电路测试时间较短,速度较快。

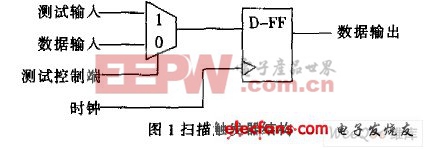

基于扫描的电路设计,主要是将待测电路内的寄存器,全部或部分用扫描寄存器来代替,让我们在对电路进行测试的时候可以轻易地控制其输入及输出,扫描寄存器最常用的结构是多路扫描寄存器,它是在普通寄存器的输入端口加上一个多路器, 如图1所示。测试控制端即多路器的选择端,数据输入端为正常的功能输入端。此外还有测试输入端、时钟输入端和数据输出端。当测试输入端为“0”时,寄存器为正常的功能输入,电路处于正常模式;当测试输入端为“1”时,寄存器为扫描输入。电路就转换成扫描模式。很明显。基于扫描的电路设计可以增加待测电路的可控制性和可观察性。这种设计方式。优点是需要额外的硬件空间较少,而且测试的效果较好,缺点是测试时间太长。造成测试时间长的原因有多个方面,我们可以通过分析基于扫描的电路设计来得到。这个缺点,正是我们想要改进的部分。

2 基于扫描的电路的基本单元

2.1 线性反馈移位寄存器(LFSR)

最简单的测试向量产生器就是由线性反馈移位寄存器(Linear Feedback Shift Registers,LFSR)来组成的。因为当时钟信号改变时,线性反馈移位寄存器内D触发器的值就会改变,此时我们就可以将这些会一直改变的值当成测试向量,送给电路做测试。

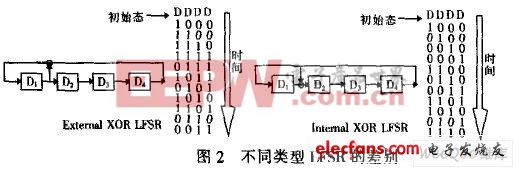

一般的线性反馈移位寄存器可以分为两类,分别是Extemal XOR线性反馈移位寄存器和Internal XOR线性反馈移位寄存器,如图2所示。这两种线性反馈移位寄存器的主要差别在于External XOR线性反馈移位寄存器的modulo一2加法器是放在电路的反馈路径上。而Internal XOR的线性反馈移位寄存器的加法器则是放在两个寄存器之问。这两种不同结构的线性反馈移位寄存器所产生出的测试向量也不一样,ExternalXOR线性反馈移位寄存器所产生的测试向量有下列特性:每个向量与下个向量之问的关系,是向量中的位分别往右移了一位。而Internal XOR的线性反馈移位寄存器由于modulo一2加法器是在寄存器之问,所以产生的测试向量看起来比External XOR线性反馈移位寄存器有更随机的特性,所以我们必须选择InternalXOR LFSR作为测试向量产生器。

评论