基于FPGA的SoC原型验证的设计与实现

摘要:在SoC开发过程中,基于FPGA的原型验证是一种有效的验证方法,它不仅能加快SoC的开发,降低SoC应用系统的开发成本,而且提高了流片的成功率。文章主要描述了基于FPGA的SoC原型验证的设计与实现,针对FPGA基验证中存在的问题进行了分析并提出了解决方案。

关键词:现场可编程门阵列;系统级芯片;原型验证;验证平台

0 引言

随着SoC设计规模的与日俱增,其功能日趋复杂,芯片的验证阶段占据了整个芯片开发的大部分时间。为了缩短验证时间,在传统的仿真验证的基础上涌现了许多新的验证手段,如SDV(Software Driven verification)、BFM(Bus Function Model)等,以及基于FPGA的原型验证技术。

因FPGA工艺及技术的发展,其速度、容量和密度都大大增加,功耗和成本在不断的降低,使得基于FPGA的原型验证得到广泛的应用。基于FPGA的原型验证可以比软件仿真速度高出4~6个数量级,而且还可以提高流片成功率,并为软件开发提供了硬件平台,加速了软件的开发速度。

本文主要论述了FPGA基原型验证的实现方法,并且针对ARM1136为内核的SoC,如何快速而有效地搭建一个原型验证平台做了详细的论述,最后还以UART为例来说明一种简单、可重用性好、灵活性强的测试程序架构。

1 基于ARM1136的SoC设计

本文验证的SoC芯片是定位于手持视频播放设备、卫星导航产品的高性能应用处理器,采用了ARM1136作为内核,ARM11在提供超高性能的同时,还能保证功耗、面积的有效性。

同时在这个架构中还采用了ARM公司的AMBA(Advanced Microcontroller Bus Architecture)总线,它是一组针对基于ARM核的片上系统之间通信而设计的标准协议。在设计中,对于一些处理数据和通讯速度要求较高的设备挂在AHB总线上,而那些对总线性能要求不高的设备挂在APB总线上。

为了能够提高一些设备间的数据传输速度,该设计加入了DMA,其支持存储器到存储器、存储器到外设、外设到存储的传输。

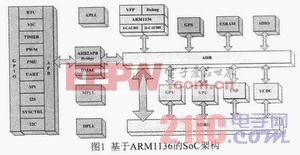

基于ARM11设计的SoC系统构架如图1所示,这个系统还包括了USB控制器、LCD控制器、图像处理单元GPU、视频处理单元VPU、GPS、I2S、通用异步串口UART、同步串口SPI、TIMER、PWM、实时时钟(RTC)、I2C总线和功耗管理单元(PMU)等。

2 FPGA原型验证平台的快速搭建

FPGA的发展为SoC的原型验证提供了巨大的发挥空间,面对复杂的SoC系统,传统的一些验证方法和单一的验证技术已经不能满足设计的要求。本文所设计的平台不仅能加快开发速度,提高流片成功率,而且还具有低错误率、快速和简易的特点,因此特别适合用于RTL代码更改频繁的设计中。

评论