基于专用数字上变频器的中频调制器

摘要:现代通信系统大部分采用数字中频调制技术产生所需要的调制信号,通过数字技术可以减小系统的体积、重量、功耗。其中在复杂的数字中频信号处理系统中,数字上变频器是产生调制信号的一个重要环节。通过对数字中频上变频基本原理和技术特点的研究,采用ADI公司AD9957数字上变频器实现了常见的几种码速率较高的调制波形。

关键词:数字上变频器;MSK;BPSK;FPGA

0 引言

根据奈奎斯特以离散量描述一个正弦波至少需要2个点的波形幅度值。但在实际的工程应用中为了保证信号失真满足系统基本要求,至少需要2.5个离散幅值点来描述一个周期的正弦波信号,若使系统调制信号达到较高的质量则需要8个离散幅值点。

例如对于载频为70MHz的数字调制系统,就必须以175~560MHz的信号速率输出数字波形。若系统中频定在100MHz就必须以250~800MHz的信号速率输出幅值。要产生这样高速率的调制波形,以目前的数字器件的技术水平存在一定困难,虽然D/A转换器的速率已经达到1GHz以上,但另一个重要的数字信号处理器部件FPGA,却很难以这样的信号速率输出信号波形所对应的离散幅值点。同时信号的高速率给FPGA同D/A转换器之间的信号连接带来了困难,为保证信号完整性的同时尽量减少高速信号带来的板内串扰,致使PCB板的设计趋向复杂化。

因此采用内核速率较高的专用调制芯片,使高速信号的产生、处理、控制、传输过程被封闭在单一芯片内完成,回避了由FPGA产生高速数据流带来的技术困难,以及PCB设计的复杂化。ADI公司针对通信市场设计的高速数字上变频器AD9957是实现高速数字调制的具有普遍适应性的一款高性能芯片。

1 AD9957数字上变频器基本技术特性

1.1 基本技术指标

AD9957内部集成了大量硬件资源,包括正交数字上变频器、滤波器、时钟倍频器、D/A转换器、增益控制器、参数寄存器、波形存储RAM、SPI接口控制器等。可通过对其内部信号参数寄存器的配置产生多种复杂波形。AD9957内核基本性能参数如下:

1 GSPS内部时钟速率,模拟输出信号最高频率为400 MHz;1 GSPS同步时钟,14 b D/A输出;相位噪声小于125 dBc/Hz(400 MHz);8个可编程键控波形存储寄存器(键控幅度、频率、相位);正交信号输入速率为250 MHz/18 b;三种可编程工作模式:正交调制方式;单音频方式;内插DAC方式。

由上述技术指标可知产生一个载频100 MHz的中频调制信号,AD9957在最高内核时钟的驱动下可以实现每个正弦波周期以10个离散幅度点输出,超过高质量波形要求的8个离散幅度点。此外8个键控波形存储寄存器,可以通过控制信号对存储波形的切换实现MSK,BPSK QPSK,8P-SK,MFSK等多种高速率的调频、调相信号。14 b的D/A可实现84 dB输出信号动态范围。在正交调制工作模式下最大基带码流的输入速率可达250 MSPS(I/Q两路总合)。

1.2 正交调制方式工作原理

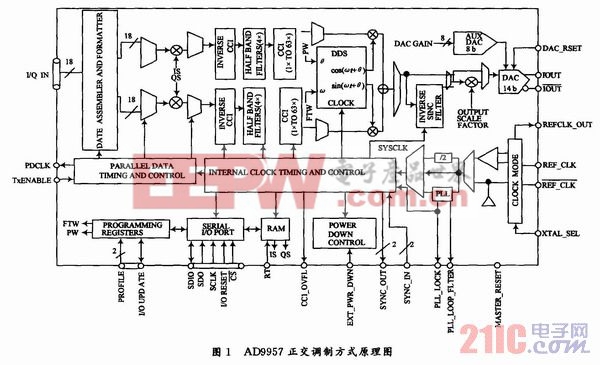

正交调制方式是AD9957的基本工作方式,如图1所示。

调制18 b I路(同相路基带码流)和18 b Q路(正交路基带码流)数据实时交替更新,一次内部采样可将I/Q数据一起提取到内部寄存器。 AD9957内部提供sin和cos的本地数字振荡器分别同I,Q输入数据流相乘,产生正交调制数据流之后相加,如下式:

![]()

正交数据流在幅度系数控制下,经D/A转换产生模拟信号输出。通过正交方式,可以实现大多数调频、调相、调幅信号的载波调制。以BPSK(二进制相移键控)信号为例,要使角频率为ωc载波在输入码流的控制下,载波相位在[0,π]之间变化,由上式可知要产生BPSK信号,正交路基带码流Q应始终为0而同相路基带码流应在正的最大值和负的最大值之间变化。当I为+MAX时sin(ω,t)的相位不变,当I为-MAX时sin(ωct)的相位反转了π。

QPSK的产生方法与此类似,但正交路基带码流不为零。而由I和Q的4种排列组成对应4种不同的载波初始相位:I=MAX,Q=0,初始相位为0;I=0,Q=MAX,初始相位为π/2;I=-MAX,Q=0,初始相位为π;I=0,Q=-MAX,初始相位为-π/2。

正交调制工作模式下AD9957具备产生较复杂的信号的能力。在输入基带码码速率低于AD9957内核时钟1/4的前提条件下,可通过控制I,Q的输入数据,使输出中频信号的频率和相位任意变化。因此可通过对输入的基带码流做前端滤波处理,使信号的频谱特性得到改善。而AD 9957通过单音频方式实现载波调制由于波形参数一次置入很难实时修正,因此不具备产生较复杂的信号的能力。

评论