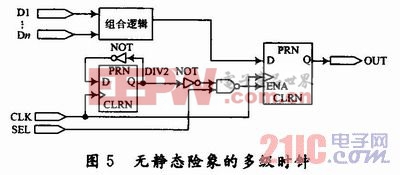

图5给出图4电路的一种单级时钟的替代方案。图中SEL引脚和DIV2信号用于使能D触发器的使能输入端,而不是用于该触发器的时钟引脚。采用这个电路并不需要附加PLD的逻辑单元,工作却可靠多了。

4 行波时钟

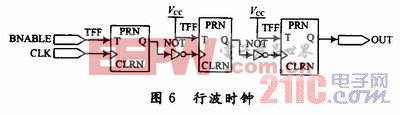

另一种流行的时钟电路是采用行波时钟,即一个触发器的输出用作另一个触发器的时钟输入。如果仔细地设计,行波时钟可以像钟一样地可靠工作。然而,行波时钟使得与电路有关的定时计算变得很复杂。行波时钟在行波链上各触发器的时钟之间产生较大的时间偏移,并且会超出最坏情况下的建立时间、保持时间和电路中时钟到输出的延时,使系统的实际速度下降,如图6所示。

评论