FPGA时钟设计

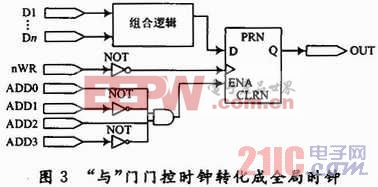

在设计中可以将门控时钟转换成全局时钟以改善设计项目的可靠性。图3示出如何用全局时钟重新设计图2所示的电路。地址线在控制D触发器的使能输入,许多PLD设计软件,如Max+PlusⅡ软件都提供这种带使能端的D触发器。当ENA为高电平时,D输入端的值被钟控到触发器中:当ENA为低电平时,维持现在的状态。本文引用地址:http://www.amcfsurvey.com/article/191103.htm

3 多级逻辑时钟

当产生门控时钟的组合逻辑超过一级(即超过单个的“与”门或“或”门)时,验证设计项目的可靠性变得很困难。即使样机或仿真结果没有显示出静态险象,但实际上仍然可能存在着危险。通常,不应该用多级组合逻辑去钟控PLD设计中的触发器。

图4给出一个含有险象的多级时钟的例子。时钟是由SEL引脚控制的多路选择器输出的。多路选择器的输入是时钟(CLK)和该时钟的2分频(DIV2)。多级逻辑的险象可以去除。例如,可以插入“冗余逻辑”到设计项目中。然而,PLD/FPGA编译器在逻辑综合时会去掉这些冗余逻辑,使得验证险象是否真正被去除变得困难了。为此,必须应寻求其他方法来实现电路的功能。

评论