基于CPLD/FPGA的多串口设计与实现

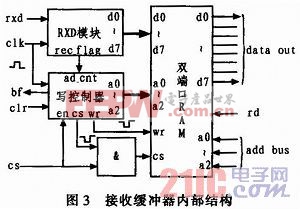

2.1.2 接收缓冲器内部结构

接收缓冲器内部由RXD接收器、地址及写控制器和双端口RAM构成,如图3所示。本文引用地址:http://www.amcfsurvey.com/article/191085.htm

1)RXD接收器

RXD接收器的作用是接收串行设备发送的数据。clk脚引入波特率时钟后,程序首先检测串行数据输入脚rxd的电平,当检测到rxd脚电平为‘0’即串行数据的开始信号后,接收器开始接收数据。连续接收8位数据后,接收到的数据将被送至d0~d7端,同时reg_flag端产生一个负脉冲信号,触发写控制器的ad_cnt端,写控制器的地址线加‘1’并同时产生双端口RAM的写操作信号,完成接收数据的存储。

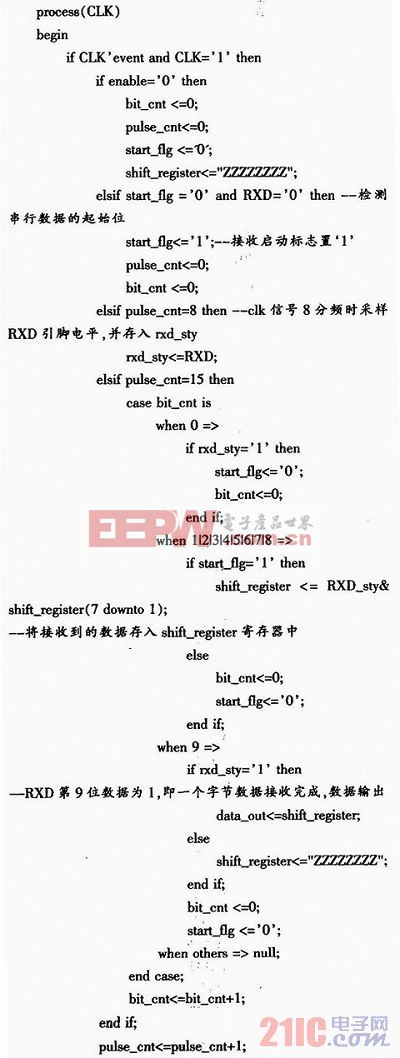

接收时,clk时钟为波特率的16倍,clk信号8分频后即串行数据位的周期的中间位置检测rxd脚电平状态,以保证串行数据准确地接收,累计计数至16分频时完成一位数据的接收。连续接收8位数据后,并判断第9位状态为‘1’时(停止位),完成一个字节的接收。RXD接收器的程序如下:

评论