基于FPGA的通用异步收发器设计

2.2 发送模块

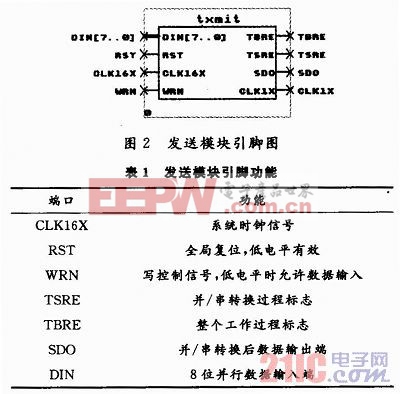

2.2.1 发送模块及其功能

发送模块主要实现对并行数据的缓存、并串转换,并把串行数据按照既定数据帧格式进行输出。发送模块的引脚如图2所示,各引脚功能见表1。本文引用地址:http://www.amcfsurvey.com/article/191039.htm

由CPU送来的待发送的并行数据,首先写入发送缓冲器TBR[7..0]。发送缓冲区中有数据待发送时,数据自动装入移位寄存器TSR[7..0]并自动完成串行数据的发送。首先传送一位起始位0,然后根据帧结构中定义的数据长度,分别串行移出TSR[7..0]中的数据,数据的低位在前,高位在后。当没有数据发送的时候,SDO管脚保持高电平。

2.2.2 发送模块功能仿真

发送器功能仿真结果如图3所示。二进制数11110000从引脚DIN[7..0]并行输入,当WRN为0时,启动发送程序,计数器开始计数,使发送器将并行数据锁存到发送缓冲器TBR[7..0],并通过发送移位寄存器TSR[7..0]逐位移位发送串行数据至串行数据输出端SDO。在数据发送过程中用输出信号TBRE,TSRE作为标志信号。当一帧数据由发送缓冲器TBR[7..0]送到发送移位寄存器TSR[7..0]时,TBRE信号为1。由发送数据缓冲器传给发送移位寄存器主要由信号TSRE控制。当TSRE为1时,表示发送移位寄存器TSR[7..0]串行发送完毕;为0时表示还没有发送完一帧数据。由仿真结果验证了发送模块的正确性。

评论