DCM和DLL使用带来的思考

一直以为DCM和DLL说得都是一个东西,使用了才知道Xilinx的时钟管理策略还真得蛮多的,虽说基本的原理上都有点大同小异。

本文引用地址:http://www.amcfsurvey.com/article/190536.htm

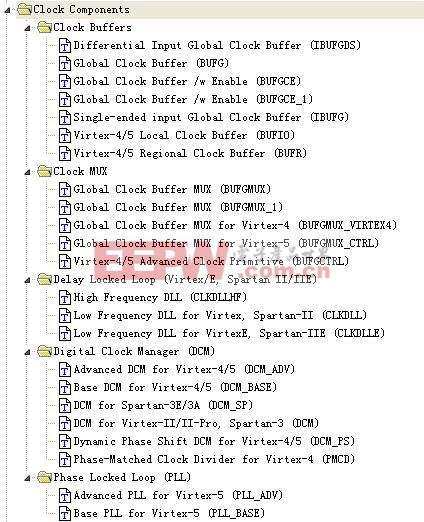

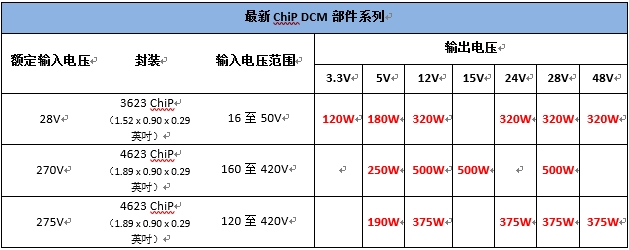

图1

先说DCM,字面上理解就是数字时钟管理单元,主要完成时钟的同步、移相、分频、倍频和去抖动等。而DLL是数字延迟锁相环的意思,是通过长的延时线达到对时钟偏移量的调节,而这个调节是通过比对反馈回来的时钟信号实现同步输出的。DCM实际上不止DLL结构这么简单,它还包括了DFSDPSDSS等组件。官方的说法如下:

The digital clock manager (DCM) component implements a clock delay locked loop (DLL), a digital frequency synthesizer (DFS), digital phase shifter (DPS), and a digital spread spectrum (DSS).

Xilinx早期的Virtex器件不提供DCM资源,只有CLKDLL,这个CLKDLL实现的时钟输出相对单一,但是基本的时钟偏斜的优化效果还是可以达到的。简单的插入语言模板进行例化就可以了。需要注意的是时钟反馈信号CLKFB不能够直接和时钟输出CLK0连接,必须让CLK0先BUFG一下。可以如下进行例化(不使用的时钟可以空着):

CLKDLL #(

.CLKDV_DIVIDE(2.0), // Divide by: 1.5,2.0,2.5,3.0,4.0,5.0,8.0 or 16.0

.DUTY_CYCLE_CORRECTION(TRUE), // Duty cycle correction, TRUE or FALSE

.FACTORY_JF(16'hC080), // FACTORY JF Values

.STARTUP_WAIT(FALSE) // Delay config DONE until DLL LOCK, TRUE/FALSE

)

CLKDLL_inst (

.CLK0(clk0), // 0 degree DLL CLK output

.CLK180(clk180), // 180 degree DLL CLK output

.CLK270(clk270), // 270 degree DLL CLK output

.CLK2X(clk2x), // 2X DLL CLK output

.CLK90(clk90), // 90 degree DLL CLK output

.CLKDV(clkdv), // Divided DLL CLK out (CLKDV_DIVIDE)

.LOCKED(locked), // DLL LOCK status output

.CLKFB(clk00), // DLL clock feedback

.CLKIN(clk), // Clock input (from IBUFG, BUFG or DLL)

.RST(!rst_n) // DLL asynchronous reset input

); // BUFG : In order to incorporate this function into the design,

// Verilog : the following instance declaration needs to be placed

// instance : in the body of the design code. The instance name

// declaration : (BUFG_inst) and/or the port declarations within the

// code : parenthesis may be changed to properly reference and

// : connect this function to the design. All inputs

// : and outputs must be connected.

// -----Cut code below this line---->

// BUFG: Global Clock Buffer (source by an internal signal)

// All FPGAs

// Xilinx HDL Language Template, version 9.1i

BUFG BUFG_inst (

.O(clk00), // Clock buffer output

.I(clk0) // Clock buffer input

);

// End of BUFG_inst instantiation

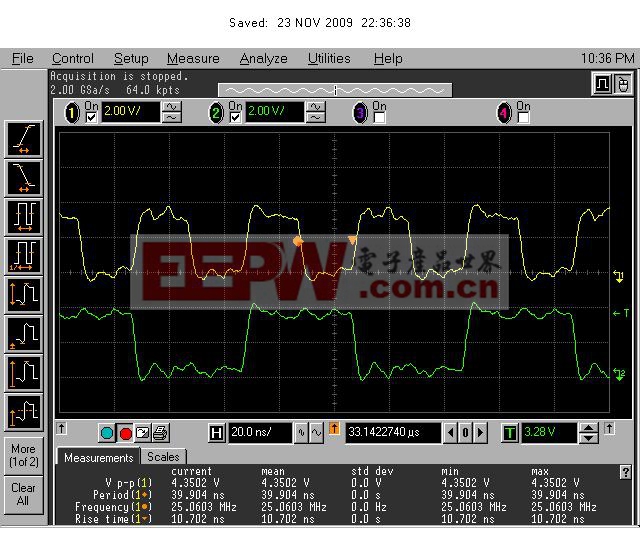

黄色:clk00 绿色:clkdv(2分频时钟)

评论