基于NoisⅡ的程控数字信号源设计

摘要:直接数字频率合成(DDS)技术在现代通信领域占据重要地位。在此提出了将Altera公司的NoisⅡ软核嵌入到FPGA器件内部来控制高性能直接数字频率合成器AD9854的方案,详细说明了系统设计电路的结构和软件设计的方法。提出了一种新的信号源控制方法,该系统具有频率分辨高、相位输出连续、可视化界面、多波形输出等优点,具有较高的市场实用价值。

关键词:NoisⅡ;DDS;FPGA;信号源

0 引言

直接数字频率合成(DDS)方式即通过可编程技术从一个标准参考时钟产生多种频率,解决了传统波形发生器高频段波形失真的缺点。而Altera公司提供的SoPC Builder工具将NoisⅡCPU软核嵌入到FPGA内部以控制高性能DDS器件AD9854,利用NoisⅡ占用芯片子资源少,成本低,可移植性高的特点。结合专用DDS的高速型和完备性,很好地解决了控制时序的不连续性。同时又大大减少处理器外围扩展元件数目,降低外围电路布局走线的复杂度,提高系统的抗干扰能力,控制灵活方便,具有较高的性价比。便于今后升级扩展。

1 系统功能的整体描述

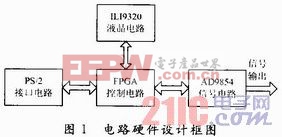

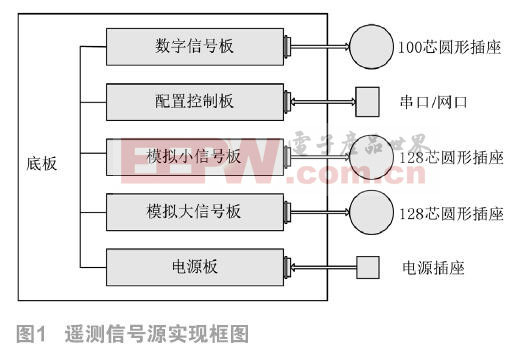

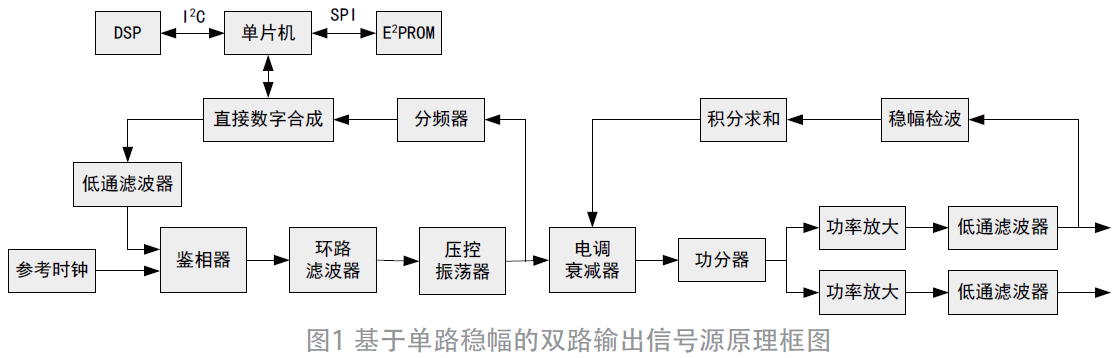

该系统主要包含3个单元:FPGA控制单元、AD9854信号产生单元和人机交互单元。系统整体框图如图1所示。系统了实现3种波形输出,可产生0~32 MHz的正弦波、方波以及FSK信号,同时在液晶上显示出相应的波形以及工作参数。外部键盘可以设置信号参数。

1.1 FPGA控制单元

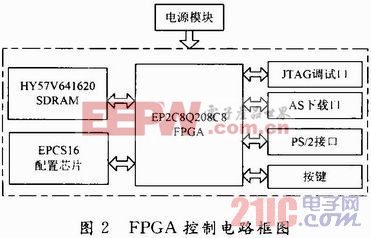

FPGA电路如图2所示。其中NoisⅡ为32位的软核CPU,外接64 Mb的SDRAM芯片和一片EPCS16的FLASH芯片。定义了一个基于Avalon总线接口的键盘控制器,用于对外接键盘进行扫描和译码。利用SoPC Builder中现有的LCD控制器IP来实现对LCD的控制。扩展了AS下载和JTAG调试口,方便程序控制。

评论