基于FPGA的高速实时数据采集系统设计

2.2.1 A/D模块

本文A/D控制模块主要就是为了控制ADS8364芯片,提供各个控制信号,以便ADS8364芯片能够正常进行模数转换、A/D转换芯片转换后的数字信号的接收并将这些数字信号写入对应的FIFO中进行缓存。

输入引脚:din(15:0):16位A/D模数转换器转换后的数字信号的输入引脚;full(5:0):6路FIFO的满标识引脚,如果该引脚有效则停止往FIFO中写入数据,如果该引脚无效则可继续向FIFO中写入数据,直到该引脚有效为止;ad:开始结束采集引脚;clk:5 MHz时钟输入引脚;rst:复位引脚。

输出引脚:dout(1 5:0):16位的数字信号输出引脚;wr_en(5:0):6路FIFO的写使能引脚;xa(2:0):ADS8364的数据读取模式选择引脚,单通道读取模式为本设计系统的读取数据模式;ad clk:5 MHz的ADS8364的时钟引脚;cs clk:开关模块时钟引脚;hold:控制AD芯片开始采集引脚;wr_clk:FIFO写时钟引脚;xcs0:ADS8364芯片片选引脚;xr:ADS8364读使能引脚;xrs:ADS8364芯片复位引脚;xw:ADS8 364芯片写使能引脚,A/D模块在Modelsim中的仿真图如图6所示。本文引用地址:http://www.amcfsurvey.com/article/190326.htm

从Modelsim仿真图可以看出,当ADS8364的读使能信号即xr为上升沿时,则表示通过A/D转换后的数字信号就转入到相应的FIFO中,从而达到数字信号的缓存作用,为后续信号实时、大量地传输到DSP进行处理做好了准备。

2.2.2 FIFO模块

FIFO(先入先出)既是最先写入的数据也是最先读出的数据的一个堆栈。FIFO具有两个单一方向的端口,然而没有像其他存储器那样,没有地址的输入:一个用于写,另一个用于读。FIFO中的数据是列队结构,因此,会出现上溢和下溢现象。当向一个满的FIFO中再写入数据时,就会出现上溢,同时如果对一个空的FIFO进行操作时,就会出现下溢。

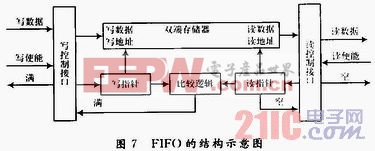

FIFO由一个双端口存储器块、一个读端口、一个写端口和一个控制逻辑模块组成,存储器模块通常采用的是SRAM,但是对某些应用也可以使用DRAM。它的结构示意图如图7所示。

FIFO是把存储器结成一个环,用内部的两个指针来寻址的。FIFO的状态并不是看两个指针的绝对大小,而是根据他们的相对大小来进行判断的。一个空的FIFO开始时把读的指针和写的指针生成相同的值,写数据时,写指针增加;读地址时,读指针增加。因此,当读指针和写指针相等时,可能存在两种情况,即空状态和满状态。在不同时钟域里对FIFO空或满状态的判断必须遵守的一个原则就是必须保证FIFO为满的情况下,不能再进行写操作,在FIFO为空的状态下,就不能再进行读操作,这就是异步FIFO设计的关键点同样也是难点。

本文用的是指针附加位比较法,这种方法是给每一个指针的前面多加一个附加位。写指针:当存储完最后一个数据单元后,将向最高位即附加位进位,除最高位外的所有位都将变为零;读指针:当读完最后一个数据单元后,也将向最高位进一位。如果两个地址指针除了最高位外其余位相同时,则表明写指针比读指针多循环了一次,此时马上停止向FIFO里面再写入数据,FIFO存储器为满状态。如果两个地址指针所有位完全相同,则表示写指针和读指针具有相同的循环次数,此时,说明FIFO存储器为空状态,此时,就会马上停止读取数据。

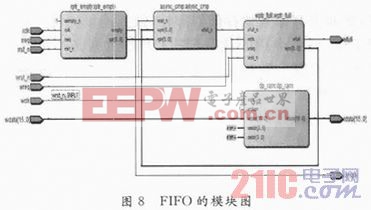

FIFO模块的输入端:wdata(15:0):来自A/D的16位写数据端;rclk:渎数据时钟端;rreq:读数据允许端;rrst_n:读复位端;wcl k:写数据时钟端;wreq:写数据允许端;wrst_n:写数据复位端。输出端:rdata(15:0):写入数据总线的读数据端;rempty:读空端;wfull:写满端。本文采用的每一个FIFO的模块图如图8所示。

评论