基于FPGA的高速实时数据采集系统设计

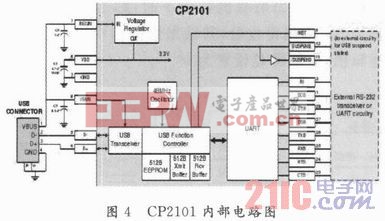

CP2101是一种高度集成的USB转UART桥接器,提供一个使用最小化的元件和PCB空间实现RS 232转USB的简便的解决方案。该芯片包含一个USB 2.0全速功能控制器、USB收发器、振荡器和带有全部的调制解调器控制信号的异步串行数据总线(UART),全部功能集成在一个5 mm×5 mm MLP-28封装的IC中。无需其他的外部USB元件。主要引脚有:

VDD:2.7~3.6 V电源电压输入或者3.3 V电压调节器输出;

:器件复位。内部端口或VDD监视器的漏极开路输出。一个外部源可以通过将该引脚驱动为低电平至少15 s来启动一次系统复位;

REGIN:5 V调节器输入。此引脚为片内电压调节器的输入;

VBUS:VBUS感知输入。该引脚应连接至一个USB网络的VBUS信号,当连通到一个USB网络时,该引脚上的信号为5 V;

D+:USB D+;

D-:USB D-;

TXD:异步数据输出(UART发送);

RXD:异步数据输入(UART接收);

CTS:清除发送控制输入(低电平有效);

RTS:准备发送控制输出(低电平有效);

DSR:数据设置准备好控制输出(低电平有效);

DTR:数据终端准备好控制输出(低电平有效);

DCD:数据传输检测控制输入(低电平有效);

RI:振铃指示器控制输入(低电平有效);

SUSPEND:当CP2101进入USB终止状态时该引脚被驱动为高电平;

:当CP2101进入USB终止状态时该引脚被驱动为低电平;

NC:这些引脚应该为未连接或接到VDD的引脚。

CP2101内部及接口连接示意图如图4所示。本文引用地址:http://www.amcfsurvey.com/article/190326.htm

2 FPGA内部逻辑设计

2.1 内部逻辑框图

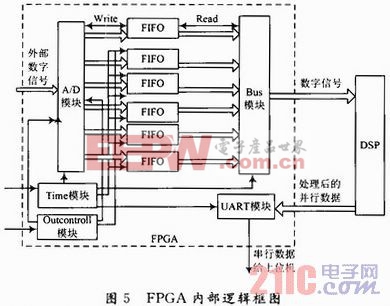

FPGA内部各个模块的逻辑框图如图5所示。

2.2 主要逻辑设计

本设计系统中FPGA内部模块主要有:Time模块、A/D模块、Outcontrol模块、FIFO模块、Bus模块和UART模块。其中,最主要的模块为A/D模块、FIFO模块和UART模块,下面就这三个模块进行描述和实现。

评论