基于FPGA的无线信道模拟器设计

2 信道模拟器的FPGA设计

FPGA采用Xilinx公司的Virtex-2p,其中芯片工作时钟为100MHz。本文设置N0=8,fm=200 Hz,

为了计算方便,将所得的值扩大32倍,也就是左移5位之后四舍五入成整数值,存入寄存器调用。所以信道模拟器的实现过程主要为各个正弦波的FPGA实现,与对应的系数相乘叠加成单径衰落,输入信号经过l个路径时延之后叠加成为输出信号。

2.1 正弦波的FPGA实现

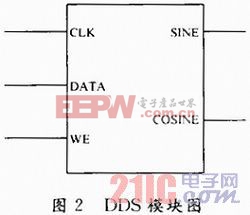

FPGA产生正弦波一般可以采用直接产生和Xilinx或者Altera利用自带DDS的IP核例化实现。FPGA直接产生是将三角函数值存入ROM中循环调用来产生正弦波,这样占用的逻辑资源比较少,缺点就是过程很麻烦而且不够灵活,模型需要8种频率的正弦波和余弦波,而且fm也可能根据需要而变化,每一次变化就需要在ROM中重新赋初值,十分麻烦。因此本文选择调用Xilinx自带DDS的IP核,通过逻辑资源换取效率。DDS的模块图如图2所示。本文引用地址:http://www.amcfsurvey.com/article/190237.htm

这样,通过控制DATA的值得到所需频率的正弦波。![]() ,其中fclk为开发工作时钟,DATA为输入的频率控制字,B为DATA的位宽,fout为所得的频率。

,其中fclk为开发工作时钟,DATA为输入的频率控制字,B为DATA的位宽,fout为所得的频率。

2.2 时延模块的FPGA实现

输入通过时延后与各路径的衰落系数相乘,然后各个路径叠加成输出信号。本文中时延采用计数分频来实现,如延迟1μs,工作时钟为100MHz,所以计算100个时钟周期后,将输入的值存入寄存器1,再计算100个时钟周期后将输入值存入寄存器2,依次类推,本为路径l设置为5,所以最终有5个寄存器存放输入值。

2.3 测试模块的FPGA实现

最后需要将算得的数据上传到Matlab进行统计分析,所以还需要FPGA串口驱动,以及Matlab打开驱动读取FPGA算完的数据。根据异步串行通信的数据传送格式,每一帧数据由起始位、数据位、奇偶校验位和停止位组成,本文只选取了数据位,一共8位。通过串/并转换接收数据,算完后存入RAM,然后调用数据,通过并/串转换传输数据。

正弦波的输出有10位,其中l位是符号位,另外9位是小数位,而系数左移5位后化成整数,在所得的整数中也有5位小数位,所以最终数据一共有19位,其中5位整数位,14位小数位。因为串口是8位一帧数据,为了运算简便,选取了5位整数位,11位小数位,舍去最后3位小数,每个数分两次传输。因为最后的数据分为实部和虚部,所以每个复数需要4帧数据传输。Matlab接收数据重新组合,还原成FPGA的计算结果。

评论