基于CPLD的PLC背板总线协议接口芯片的设计

设计了一组基于CPLD的PLC背板总线协议接口芯片,协议芯片可以区分PLC的背板总线的周期性数据和非周期性数据。详细介绍了通过Verilog HDL语言设计状态机、协议帧控制器、FIFO控制器的过程,25MHz下背板总线工作稳定的试验结果验证了协议芯片设计的可行性。

本文引用地址:http://www.amcfsurvey.com/article/190097.htm可编程逻辑控制器(PLC)主机是通过背板总线支持扩展模块的连接, 背板总线是PLC 主机同I/O扩展模块之间的高速数据通路,支持主机和扩展模块之间的I/O 数据刷新。背板总线的技术水平决定了PLC 产品的I/O 扩展能力,是PLC 设计制造的核心技术。目前,PLC 大多采用串行通信技术实现背板总线,串行总线引线少、硬件成本低,跟并行总线相比不容易受干扰,串行总线可以提高在恶劣的工厂和工业环境下自动化设备的可靠性。用于串行通信技术的可选类型包括I2C、UART、SPI、USB 和以太网等,一般来说,很多作为PLC 主芯片的单片机自身都集成了这些外设部件。但是单片机内部集成的I2C、UART、SPI 外设通信速率太慢,根本不能满足底板总线的通信速度要求。USB 和以太网的通信速度虽然很快但由于它们都是通用的接口,在通信协议处理时需要单片机的干预, 单片机处理数据速度较慢,因此整体通信速度仍然很慢。一台大型的PLC 采集上千点I/O 数据的时间一般不到1ms,要满足如此高速的通信要求必须设计专门的背板总线。

1 背板总线工作原理

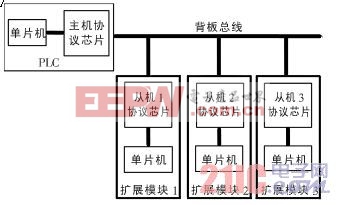

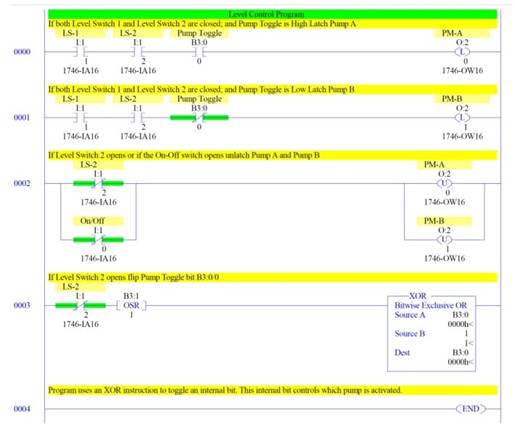

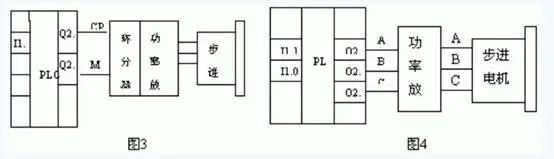

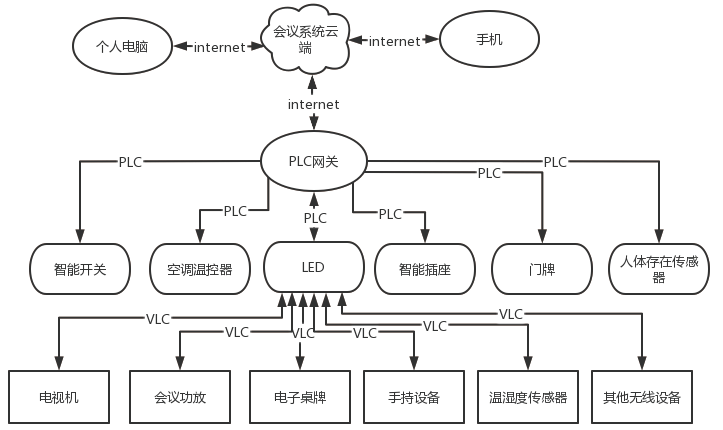

如图1 所示,基于背板总线的数据通信流程如下:

(1)PLC 主机的命令通过主机协议芯片发送到背板总线;(2)从机协议芯片把接收到的命令给扩展模块的单片机, 某一个扩展模块的单片机做出应答,通过从机协议芯片把应答数据送往背板总线;(3)主机协议芯片收到应答数据,并送往PLC主机的单片机。

图1 背板总线通信框图

PLC 主机发往背板总线的数据可以分成两类:一类是I/O 刷新数据,具有周期性,数据交换非常频繁;另一类是诊断性数据,具有非周期性,出现机会较少。

2 协议芯片设计

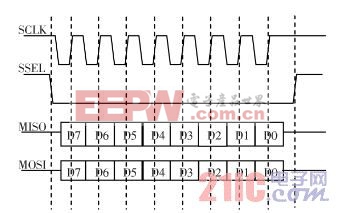

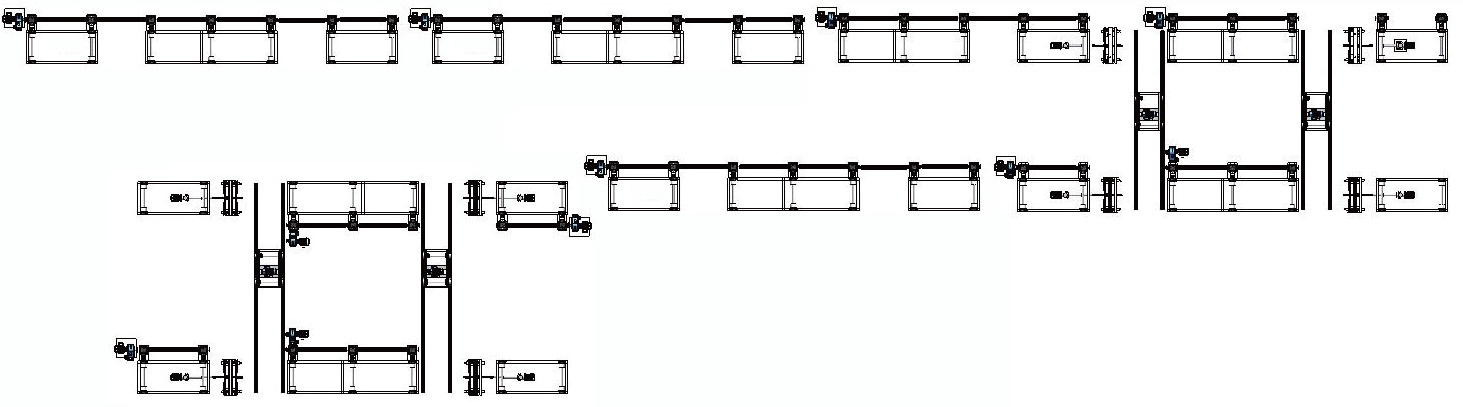

本设计定义背板总线采用类似SPI 串行通信的规格,用于通信的引线共4 根,包括时钟信号SCLK、片选信号SSEL、写数据引线MISO 和读数据引线MOSI;支持主机和从机同时收发数据,数据位格式如图2 所示,数据帧在SSEL 信号为低电平时传输。

图2 背板总线数据规格

评论