基于消息机制的片上多处理器系统的研究

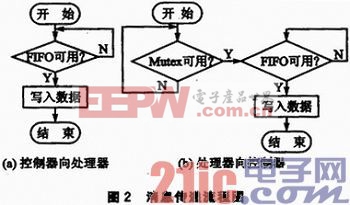

2.2.1 控制器到处理器方向

控制器到处理器方向的连接属于一对多的模式,每条通路各自独立,因此该方向上的传递比较简单,由控制器直接向目标FIFO写入数据即可。该方向的传递流程图如图2(a)所示。本文引用地址:http://www.amcfsurvey.com/article/189737.htm

2.2.2 处理器到控制器方向

处理器到控制器方向的连接属于多对一的模式,当处理器同时有消息要传递给控制器时会引起冲突。为解决该冲突,系统引入了互斥核。因此该方向上的消息传递时需要先锁定互斥核,才能向控制器的FIFO写入消息数据。该方向的传递流程图如图2(b)所示。

2.3 消息的读取

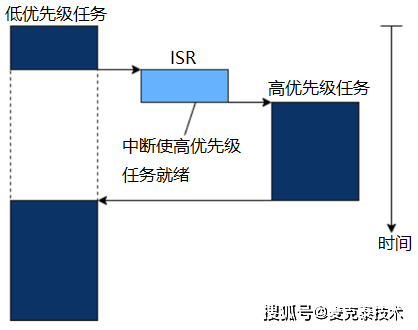

消息的读取过程为处理器从消息存储器FIFO读出数据的过程。由于采用的是双端口FIFO,数据的写入与读取可同时进行。但由于处理器可能存在中断、写入与读出速率不一致等原因,因此消息的读取采用异步读取的方式,即判断FIFO中的数据个数,先读取消息的前两个字节,获得该消息的长度,然后根据该长度等待消息传递完毕,再一次性读取剩余消息数据。

2.4 消息的处理

消息读取完之后,首先发送确认消息给发送者,表示成功收到了消息。然后根据洧息中的类型跳转到该类型的处理函数,接着再根据消息中的子类型跳转到该子类型的处理函数。最后,当任务执行完之后发送任务结束消息。

2.5 数据移动

当系统中有大量的数据需要移动时,为了减少系统的开销,加入DMA核。数据的移动由DMA核控制,而DMA核由控制器进行控制。因此,从处理器如果有移动数据的需要,需要用消息先通知控制器,然后由控制器控制DMA进行移动。图3为控制器利用DMA进行数据移动的流程图。

2.6 容错性设计

当系统长时间运行时,不排除处理器出现问题的可能性,因此需要引入容错性设计,保证系统能正确运行。

首先,主控制器中定义一个从处理器列表。从处理器初始化完成时,发送初始化完成消息,主控制器对发送消息的从处理器进行登记,并添加到列表。

接着,主控制器中定义一个任务结构,包含任务所属的组、任务ID、任务允许最长处理时间、任务开始处理的时间等字段。运行时,主控制器根据事先设计的程序生成任务列表,然后根据从处理器列表分配任务,并记录任务处理开始时间。

然后,主控制器反复查询任务列表,检查任务时间。当发现任务超时,则重新分配该任务,使得系统仍能正常工作,并将处理该任务的从处理器从列表中别除,发出警报。

3 实验与结果

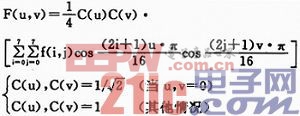

为了验证该系统的可行性及性能,本文采用JPEG编码器(以DCT变换为基础的有损压缩算法)作为该系统的测试程序。DCT算法的大致流程为:对于一块最小数据处理单元(MCU),先把数据从空间域变换到频率域,从而去除数据的冗余度;量化器用加权函数来产生对人眼优化的量化DCT系数,同时熵编码器将量化DCT系数的熵最小化。

其中前向DCT的变换公式如下:

评论