基于FPGA的面阵CCD成像系统设计

摘要:采用SONY行间转移型面阵CCD ICX415AL作为图像传感器,设计了一款新型CCD成像系统。以Altera公司的FPGA芯片EP1C12F256作为时序发生器产生CCD驱动信号。采用相关双采样技术滤除了视频信号中的相关噪声,提高信噪比。在QuartusⅡ9.1开发环境下采用VHDL编程,并利用Modelsim SE 6.5仿真软件进行访真测试。实验结果表明,所设计的时序满足ICX415AL的时序要求,在29.5 MHz的时钟驱动下,每秒输出50帧图片,能满足高速跟踪要求。

关键词:行间转移型面阵CCD;驱动时序;相关双采样;FPGA

0 引言

CCD(Charge Coupled Device)是20世纪70年代初发展起来的新型半导体集成光电器件,它可以把通过光学镜头投影到其上的景物可见光信号转换成比例的电荷包,并在适当的时钟脉冲的驱动下进行定向转移,从而输出成为电压视频图像。CCD具有集成度高、功耗小、体积小、工作电压低、灵敏度高等优点,目前已广泛应用与空间遥感、对地观测等领域。

按结构分类,CCD可分为线阵CCD和面阵CCD,而面阵CCD按排列方式又可分为全帧转移(Full Frame)CCD、帧转移(Frame Transfer)CCD以及行间转移(Interline Transfer)CCD。三种类型的CCD各有优缺点,其中行间转移CCD不需要机械快门,速度最快,最适合用于观测快速运动的物体。本文设计了一种行间转移型面阵CCD的高速驱动电路。

1 行间转移型面阵CCD的结构和工作模式

本设计采用的是SONY公司的ICX415AL型号CCD芯片,ICX415AL是行间转移型面阵CCD,对角线为8 mm,尺寸为8.3 μmx8.3 μm,总像元素为823(H)×592(V),有效像元为782(H)x582(V)。它不仅具有高灵敏度、低暗电流的特性,而且还具有优秀的抗开花技术。ICX415AL还具有连续可变的电子快门功能,可以通过控制曝光时间,获得不用曝光条件下的图像。

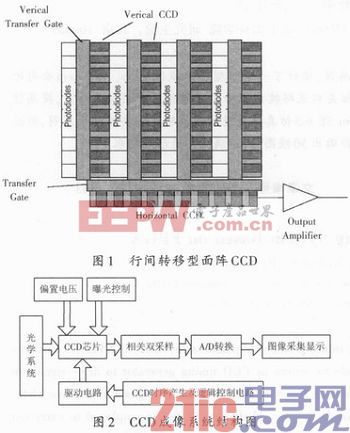

ICX415AL的结构如图1所示。其中,感光单元与存储单元相邻排列,相当若干个单边传输的线阵CCD按垂直方向排列,在积分时间结束后,感光单元电荷转移到相邻的存储单元,在垂直转移脉冲V1,V2,V3的共同作用下一行一行的转移至水平移位寄存器,在水平转移脉冲H1,H2和复位脉冲RG的共同作用下经放大器读出。

2 行间转移面阵CCD的驱动电路设计

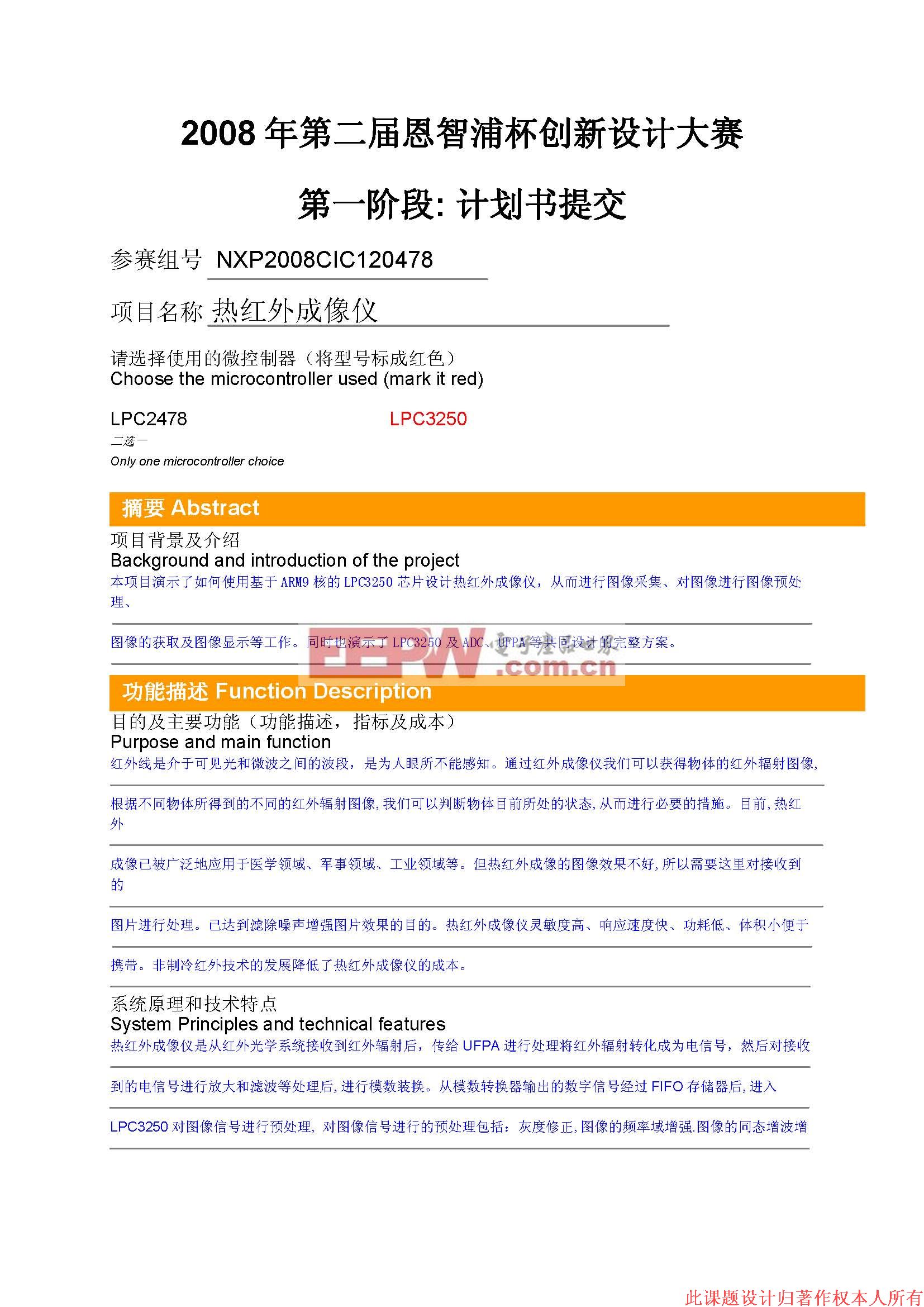

整个电路设计如图2所示,它主要包括偏置电路、时序驱动电路、视频信号处理单元等。下面分别介绍这几个部分。

ICX415AL偏置电路设计包括电源电压以及各种驱动时序电压。经仔细分析得出,CCD的垂直转移信号电压为-7.5 V,0 V,15 V三个级次,水平移位信号和复位信号电压为5 V,基底信号电压为22.5 V,FPGA供电电压为3.3 V。综合CCD供电系统要求,选用24 V作为外部电压,使用YD12-24S15芯片获得15 V和-12 V电压,利用YDl6-24S05芯片获得5 V电压。分别将-12 V和5 V电压经过芯片LM2991和芯片LT1764EQ转换为-7.5 V和3.3 V电压,这样就获得了整个电路所需要的电压。

时序驱动电路的设计比较复杂,对成像效果至关重要,因此,时序驱动电路的设计是整个系统的关键。ICX415AL芯片有3种驱动模式:逐行扫描模式、场读出模式和中心扫描模式。其中逐行扫描模式具有较高的分辨率,且在29.5 MHz的时钟驱动下可以达到每秒50帧图像,满足设计的需要,因此本设计采用逐行扫描模式。在该模式下,CCD需要7个驱动信号,垂直转移时钟V1,V2,V3,水平转移时钟H1和H2,复位时钟信号RG,以及控制曝光时间的基底时钟SUB。CCD的一个周期包括感光阶段和转移阶段。在感光阶段,给基底提供一个时钟信号,在信号高电平期间,CCD处于偏置阶段,开始收集电荷,储存电荷的多少取决于外界光亮度以及曝光时间。当垂直转移时钟V1,V2,V3出现一个如图3所示的三相电平信号时,感光阶段结束,成像单元电荷以电荷包的形式转移到相邻的存储单元。转移阶段分为垂直转移和水平转移。垂直转移包含625个循环,每循环一次,电荷沿垂直方向移动一行,最后一行移入水平寄存器,然后在水平移位时钟H1,H2和复位时钟RG的作用下完成944个循环,每次循环输出一个像元信息。复位时钟RG用于将浮置扩散节点的电荷清除掉,以便能准确测量下一个点荷包。

fpga相关文章:fpga是什么

电荷放大器相关文章:电荷放大器原理 热成像仪相关文章:热成像仪原理

评论