利用数字电位器实现数控低通滤波器

数字电位器是一种应用普遍的器件,以下介绍如何使用数字电位器构建一个可调带宽的低通滤波器。

2 一种简单的低通滤波器

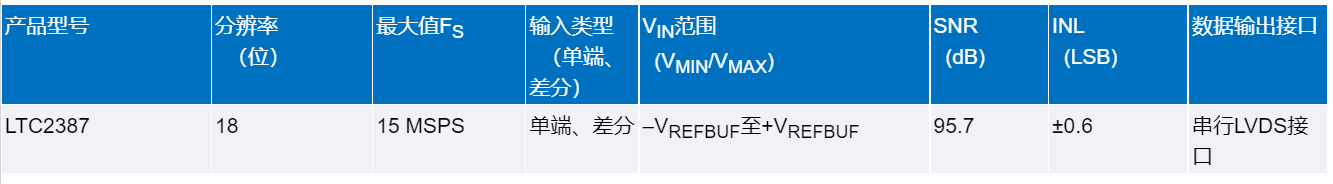

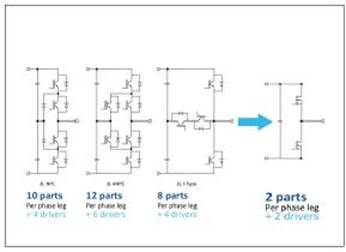

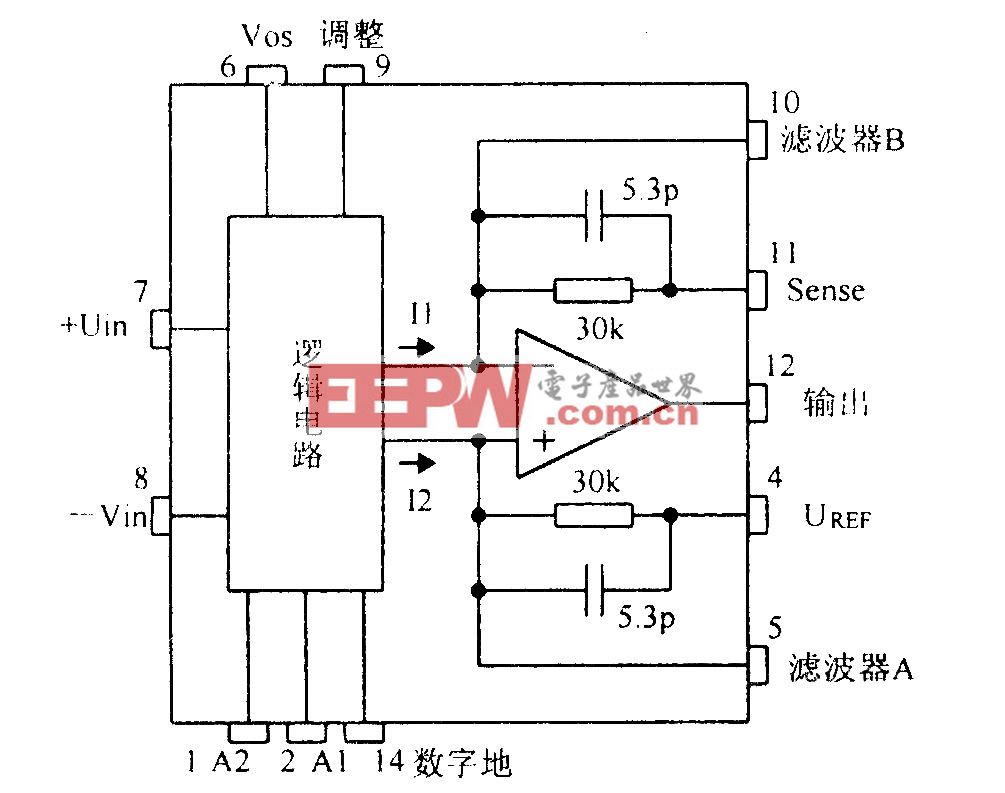

由DS3903构成的音频低通滤波器如图l所示。该电路采用单电源供电,电源电压范围为2.7~5.5 V。包含一级前置衰减,5.0 V供电时可处理5.0 VP-P(1.77VRMS)输入。为了产生一个双极点(极点在同一频点)低通滤波器(每10倍频程衰减12 dB),电容C3必须是C2的2倍以上,可变电阻POTO和POTl设置相同值,则截止频率(fC)计算如下:

![]()

其中,RPOT是可变电阻POT0和POT2设置对应的电阻值。

该电路的输入部分(Cl、U1一POTl、U2A、Rl和R2)是音量控制电路,还可将音频信号的直流偏置到VCC/2,使信号在未嵌位的条件下通过数字电位器和运放器,在任何供电电源下,电路都能够处理最大信号摆幅。因此,该设计在2.7 V至5.0 V下工作性能良好。输出直流电平保持在VCC/2,除非在正常输出以外工作,电平将偏移到不同工作点。

对于已限定工作范围的应用,可以去掉输入级电路,采用直接耦合的方式连接到滤波器。去掉输入电路后,输出信号只是经截止频率为fC的双极点滤波器滤波后的信号,而输入信号的直流分量则直接旁路到输出端。

通过更改电容或选择不同端到端电阻的数字电位器,该电路的截止频率可设置为500 kHz。

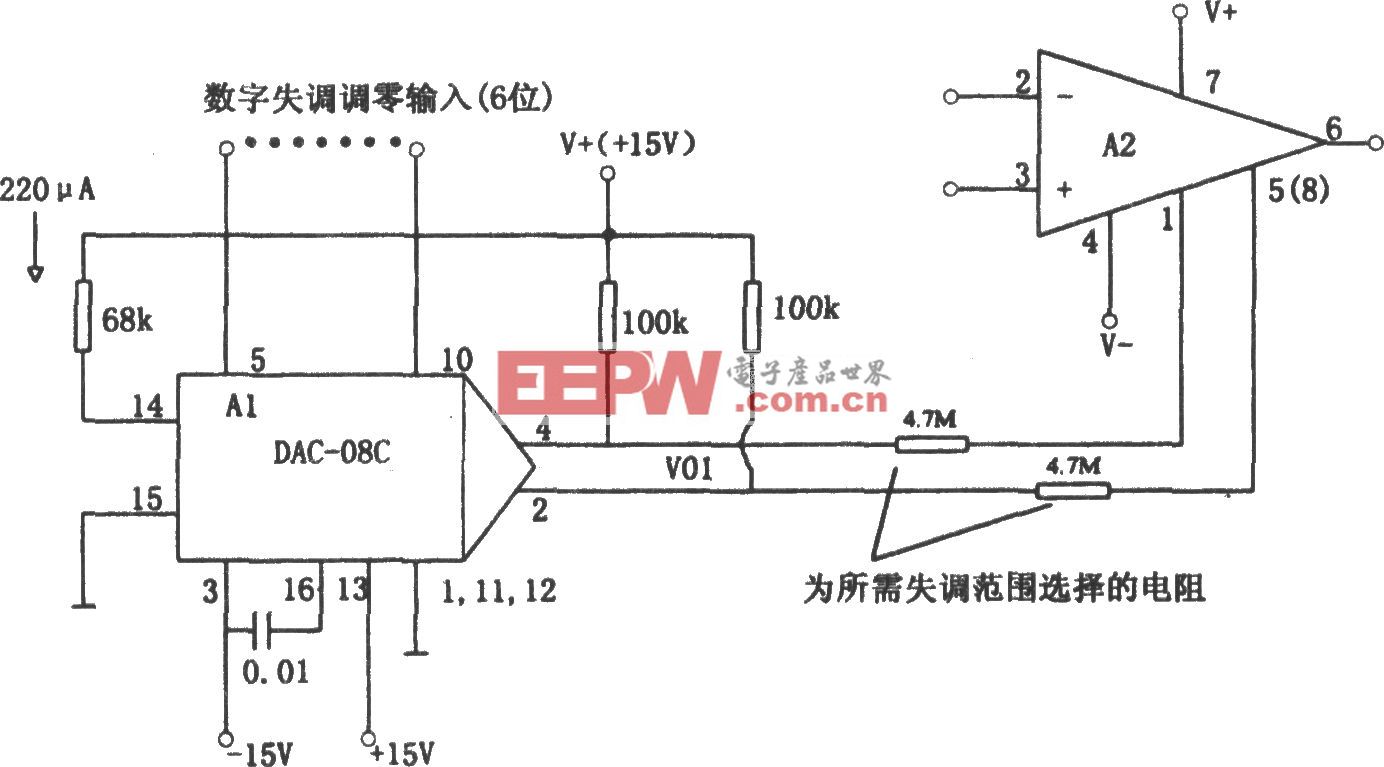

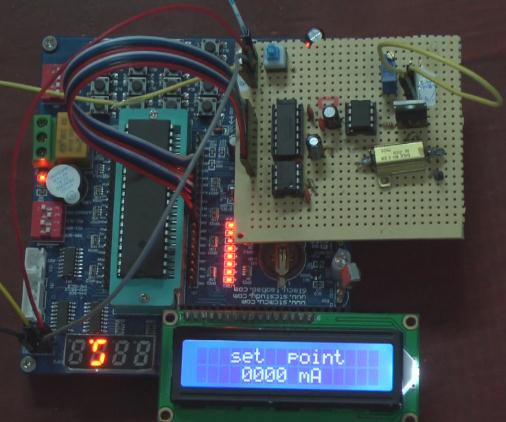

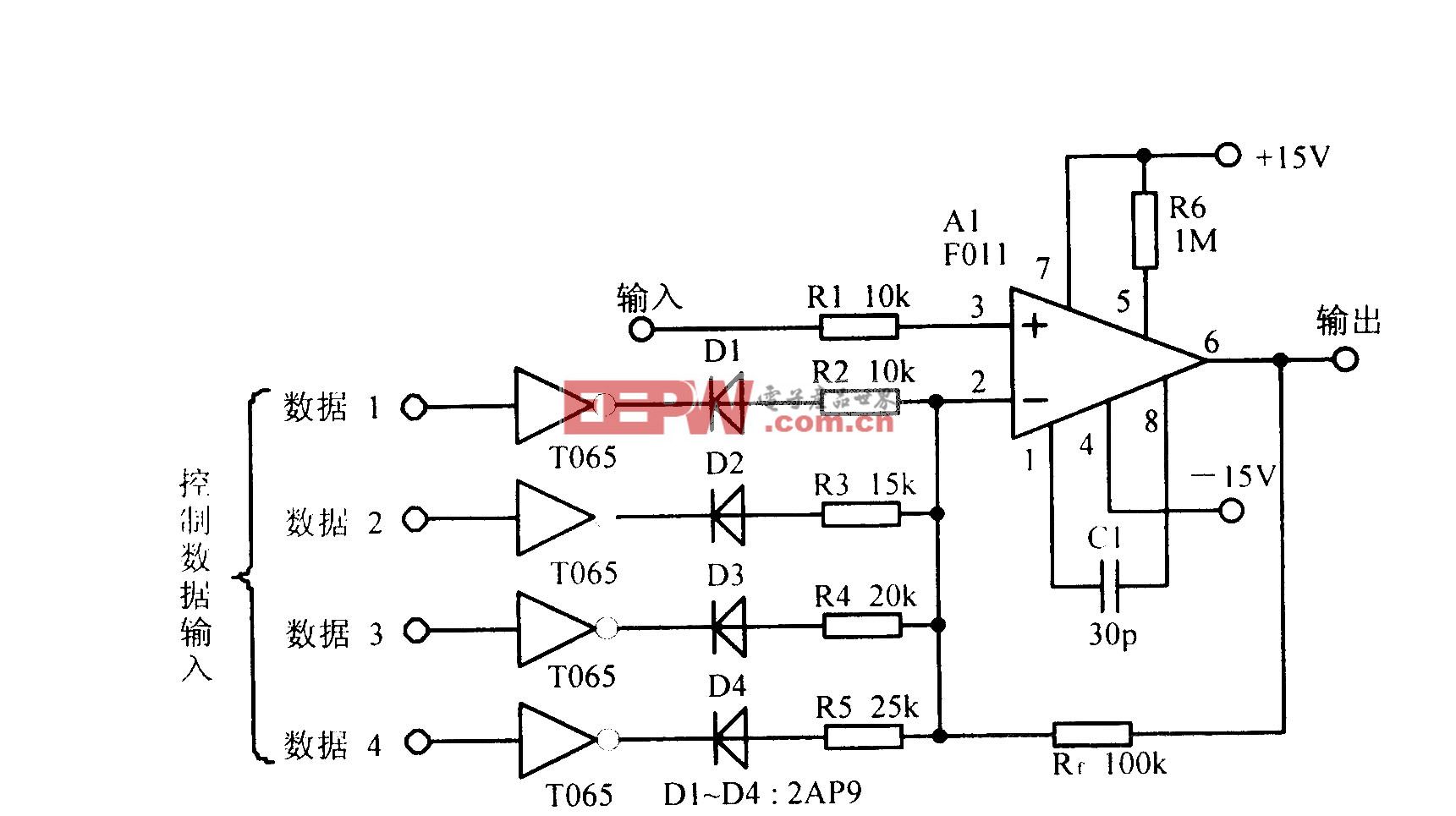

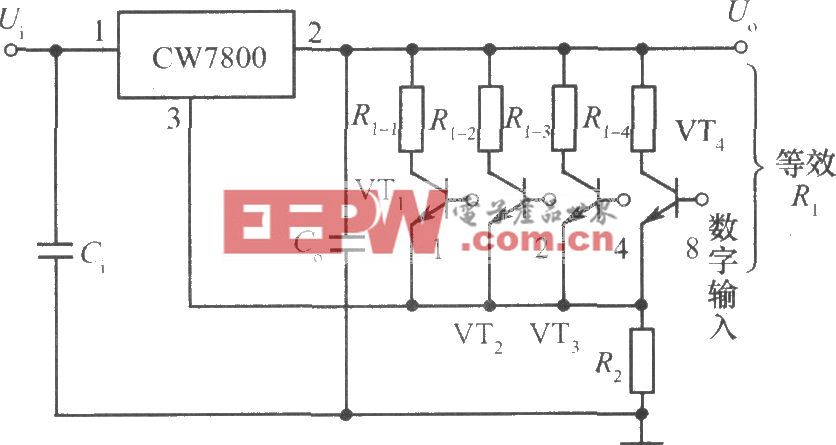

用于计算RPOT的数字电阻模型如图2所示,对于指定位置,相应的开关将闭合而其他位置的开关则开路。电位器每递增一个单元位置,电阻将相应增加LSB(对DS3903,10 kΩ/128=78Ω),最高抽头位置除外,最高抽头位置为电位器电阻的并联组合,则引起非线性。通过下式计算RPOT:

![]()

其中:RLSB是端到端电阻除以抽头数;RW是滑动端、电阻;n是电位器的编程位置;a是数字电位器的总抽头数。

图3所示给出了DS3903 10 kΩ电位器的RPOT电阻值与抽头位置之间的关系图,假定端到端电阻为10 kΩ,滑动端电阻最小值是500Ω。这两个参数都会对滤波特性产生显著影响,但主要影响的是截止频率的最小值和最大值,实际截止频率可以在其最小值和最大值之间调节,选择适当的电容值即可将截止频率设置在可调范围内所要求的频点。

3 数字电位器设计考虑

滤波电路选择数字电位器时需要考虑以下几个因素。

使用数字电位器的最大限制是电位器端点的电压,通常该电压必须保持在VCC和GND之间,以避免ESD结构内部的二极管将音频信号嵌位。当VCC在规定的范围(2.7~5.5 V)内时,DS3903的ESD结构允许输入信号处于6 V与GND之间,这一特性对于要求输入信号大于VCC的应用非常灵活。但是,在图l所示电路中并未处理6.0 VP-P信号,因为运放电源低于6 V时将会嵌位信号。如果运算放大器能够采用更高的电压供电,即可使用DS3903的大信号处理功能。

电位器抽头的变化形式(线性或对数)决定了电路截止频率的线性调节或对数调节形式。对于图l所示音频范围的滤波电路,为保证在40~800 Hz之间提供尽可能多的截止频率设置,采用线性电位器比较合适。

电位器的分辨率(如128或256抽头)决定了截止频率的调节精度,抽头数越多,截止频率的调节精度也越高。对于音频应用,不太可能使用64或128抽头以上的电位器来设置低通滤波器的截止频率。对于宽带应用则要求更多的电位器抽头。

一些数字电位器采用非易失存储,能够在没有电源供电时保持抽头位置。这种特性可用于保存校准后的滤波器位置,而在上电时不再调整滤波器设置。易失电位器总是从一个预置位置启动,电路在被修改之前将一直保持默认位置。

数字电位器的端到端电阻和滑动电阻具有较宽的公差,图l所示电路中的两个电阻(POTO和POT2)则保持相等,因为这两个电阻制作在同一硅片上。电位器的实际阻值差别较大,通常端到端电阻的变化范围是±20%,但它们的相对值基本保持稳定。

另外,数字电位器内部也具有一定的寄生电容,这会限制最大截止频率。截止频率大于500 kHz时,不推荐使用10 kΩ的数字电位器,也不建议将50 kΩ数字电位器用于100 kHz以上的设计或将100 kΩ的数字电位器用于50 kHz以上的设计。对于音频应用,所选择的电位器能够提供足够的带宽,但对于宽带应用,必须慎重考虑这一因素。

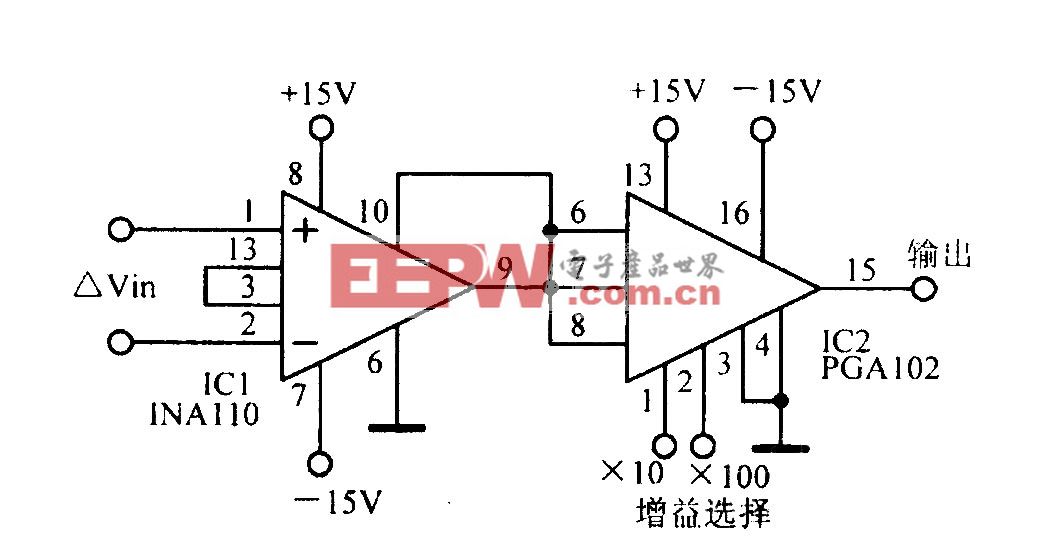

4 运算放大器的选择

该电路对于运算放大器的主要设计考虑是最小稳定增益和输入、输出电压摆幅。输入级接收信号并将其偏置在VCC/2直流电平,滤波器本身是单位增益放大器。为保证可靠工作.放大器必须是单位增益稳定。另外,还需选择具有满摆幅输入、输出的运算放大器,以处理接近电路供电电压的输入信号。

5 结语

数字电位器可用于构建数控低通滤波器.本文中的双极点滤波器能够在音频应用中提供良好性能,选择不同的电容、电位器值可以调整滤波器的截止频率,最高可达500 kHz。

评论