闪变信号电路的设计与实现

随着我国国民经济的发展,电力网负荷急剧增加,特别是冲击性、非线性负荷所占比重不断加大,使电网电压产生波动和闪变,严重影响了电网的电能质量。因此,研究电压波动与闪变、积极采取措施保证电能质量己成为当前供电部门的一项重要而紧迫的任务。然而如何得到闪变信号成为重要问题,因此,标准闪变信号电路的研究是基于SOPC的电压波动和闪变检测与分析的重要内容。

本文提出一种全数字化技术的闪变信号电路,主要研究了该电路的原理、关键参数设计准则,并给出了试验结果。

1 闪变信号电路的构成与原理

1.1 电路构成

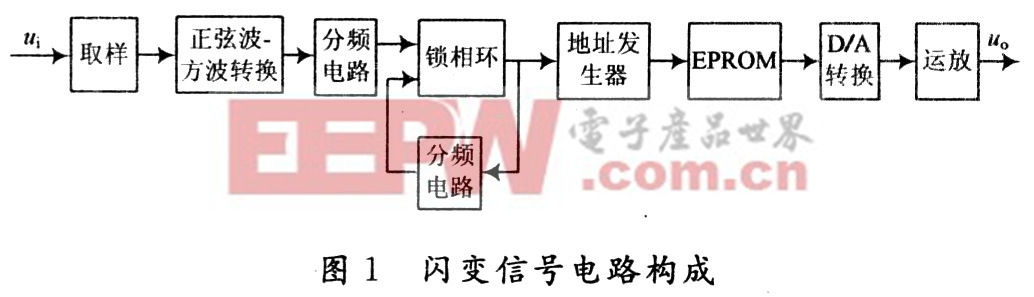

闪变信号电路由电网电压取样和正弦波一方波转换电路、倍频电路或分频电路、时钟信号形成电路(包括锁相环和分频电路)、相位同步电路(即地址发生器清零信号形成电路)、闪变信号产生电路(包括EPROM,D/A转换电路和运算放大器)等五个部分组成,如图1所示。其基本思想是先将电网电压ui变换成一个电压方波信号,将电压方波信号分频后(如n=4)得到基准电压方波信号(频率即为12.5 Hz),输入到锁相环,锁相环输出信号经m分频电路(如m=1 024)后再送回锁相环,作为基准电压方波信号的比较信号。当锁相环处于锁定状态时,锁相环输出频率为基准电压方波信号m倍的时钟信号。该时钟信号送人地址发生器,然后依次读取出事先固化在EPROM中的数字化的标准闪变信号,再经过D/A转换和运算放大器,变换成闪变信号电压。

1.2 电路原理

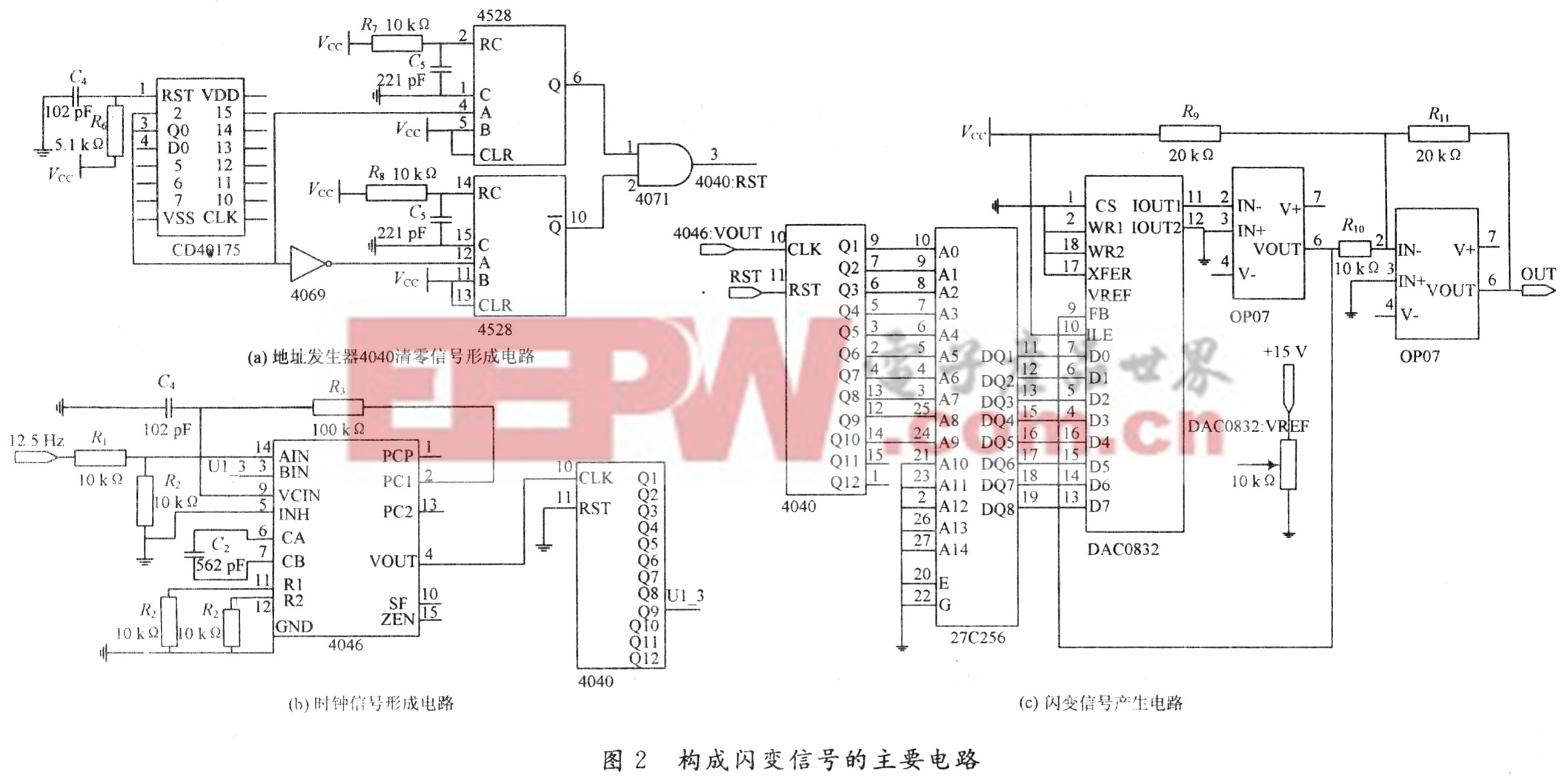

闪变信号电路的主要电路如图2所示。

电网电压取样与正弦波一方波转换电路由变压器取样、过零比较器组成,其输出的电压方波信号与电网电压同步。

相位同步电路即4040清零信号的形成电路,如图2(a)所示。将基准方波电压信号送入D触发器40175分频,输出6.25 Hz的方波(保证一周产生一次清零信号),再将其信号及其经过非门4096后的反相信号一起送入单稳态触发器4528,经或门4071后得到4040的清零信号,以实现4040的1 024分频计数,从而保证对EPROM中数据的正确读取。

时钟信号形成电路如图2(b)所示。将基准电压方

波信号输入锁相环,由锁相环输出电路所需的时钟信号。在锁相环的锁定状态下,该时钟信号频率为基准电压方波信号频率的1 024倍。该时钟信号经分频器4040实现1 024分频,所得信号作为锁相环的比较信号。将此时钟信号送人地址发生器4040。

闪变信号产生电路由地址发生器4040,EPROM27C256,DAC0832和OP07组成,如图2(c)所示。其核心是EPROM27C256和DAC0832。可事先由Matlab编程产生的一个周期的闪变信号,再由Matlab进行1 024分频离散采样,算好其幅值后按序排成数据表存入EPROM中。

锁相环输出的时钟信号输入到地址发生器4040,4040顺序扫描存入EPROM中的数据表,代表闪变信号幅值的8位二进制数被送到DAC0832,将数字量转换成模拟量输出。周而复始,产生一串阶梯闪变波形。由于DAC0832为电流型器件,因此必须与运算放大器连接,构成D/A转换器。

2 关键电路参数设计

锁相环CD4046是整个电路关键器件之一,其锁定范围和外围电阻R4,R5及电容C2有很大关系。R3和C1构成了锁相环CD4046的外接低通滤波器。

DIY机械键盘相关社区:机械键盘DIY

评论