一种高速低压用增益增强型运算跨导放大器设计

在高性能模拟集成电路,诸如开关电容滤波器、∑-△调制器和流水线A/D转换器中,常常需要高直流增益、高单位增益带宽的运放来同时满足系统对精度与速度的要求。高增益要求运放采用多级、长沟道器件,小的工作电流;而高速则要求运放采用单级、短沟道器件,大的工作电流。增益增强技术的提出解决了这对矛盾,提高了运放的直流增益而又不影响其高频性能。然而,零极点对(doublet)的存在会影响运放的建立特性[1,2]。通常,消除doublet影响的方法是提高其发生的频率,但若过高的doublet发生频率将导致系统的不稳定[3,4]。

1 运放的设计和优化

1.1 运放的结构选择

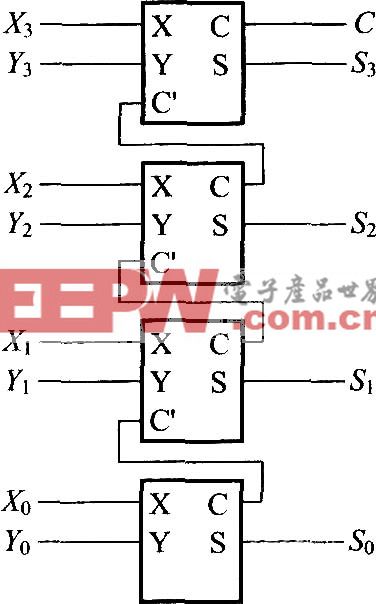

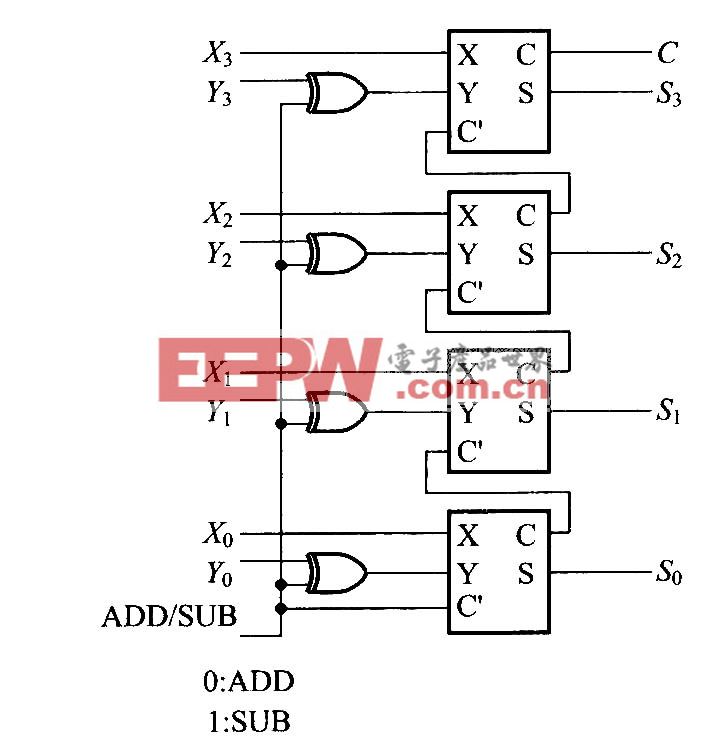

目前流行的运算跨导放大器(OTA)结构中,套筒结构有最好的性能,但输出摆幅

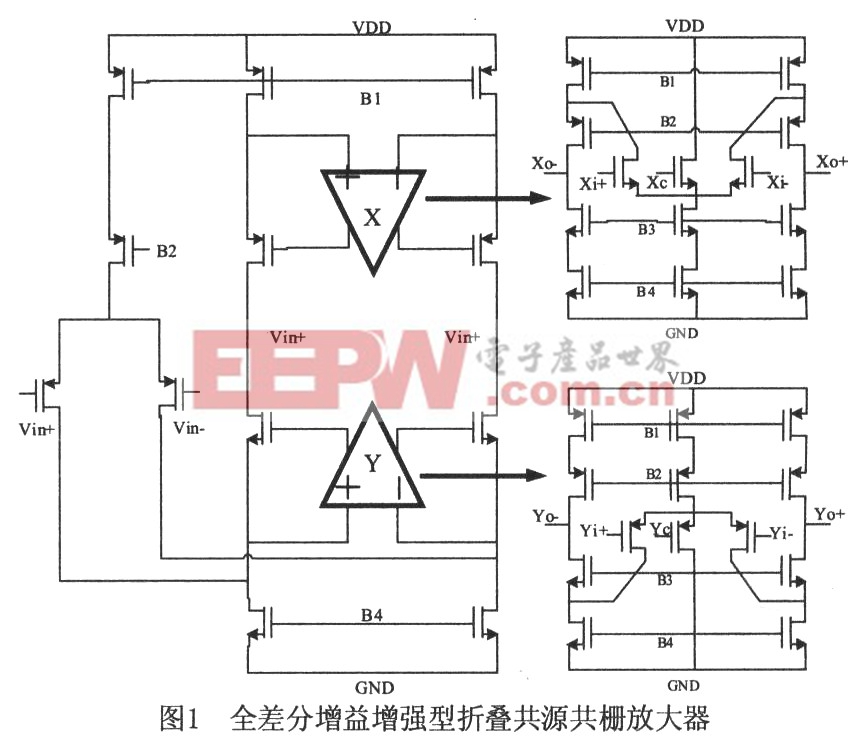

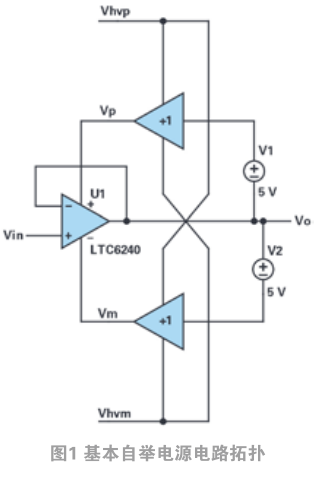

受限,不适合用于低压设计。折叠共源共栅结构有更大的输出摆幅以及可以使输入和输出短接,共模输入电平更容易选取,所以得到了广泛的应用。本运放采用折叠共源共栅结构,总电路如图1所示。(参见右栏)输入管选用PMOS管,因为PMOS管的载流子迁移率低,所以要获得相同的速度和增益,需要更大的电流和更大的尺寸,但因为它的折叠点在NMOS处而NMOS的尺寸要小于流过相同电流的PMOS的尺寸,所以折叠点的寄生电容比较小,折叠点带来的极点高,有较好的频率特性。另一方面,PMOS输入管优化了1/f噪声。

1.2 建立时间分析及优化

采用共源共栅结构的增益增强技术提高了直流增益,却没有显著影响高频性能,然而由于零级点对的存在,影响了运放的瞬态建立特性。下面主要分析运放建立特性,来优化建立时间。

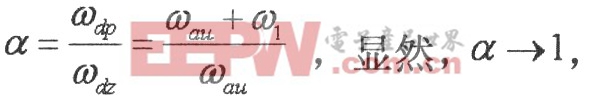

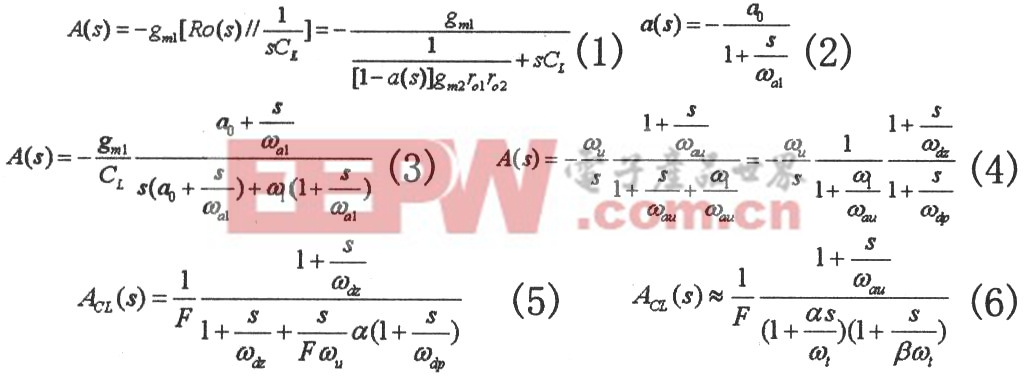

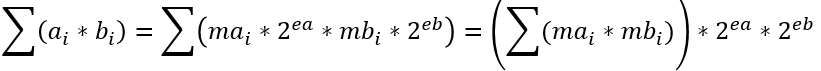

首先,应考察辅助运放引起偶对的原因。在忽略寄生电容作用的条件下,单极点性质的增强型运算跨导放大器(GBCA)增益传递函数为式(1),若辅助运放采用式(2)的单极点模型近似,a0》1,得到式(3),代入ωau=a0ωa1的条件,在ω》ωa1的频率范围下,开环增益为式(4),由内部反馈环路形成的一对偶对分别为ωdz=ωau,ωdp=ωau+ω1。以偶对中数值较小的零点ωdz为参照,偶对的分离系数α为 该零点的分离度与辅助运放的单位增益带宽和主运放的主极点频率密切相关。在以上简单近似条件下,由于ωau与ω1无关,则当单调增加辅助运放带宽使ω》ωa1时,形成的偶对相互间越来越靠近,对系统相位的影响可以忽略,而对瞬态特性的影响必须以闭环系统进行分析。对于F反馈系数及以上开环系统构成的闭环系统,开环系统的偶对将变成闭环系统的偶对。在ω》ωa1的频率范围下,有式(5),设闭环系统在主次极点分离条件下的主极点频率为ωi=Fωu。考虑到

该零点的分离度与辅助运放的单位增益带宽和主运放的主极点频率密切相关。在以上简单近似条件下,由于ωau与ω1无关,则当单调增加辅助运放带宽使ω》ωa1时,形成的偶对相互间越来越靠近,对系统相位的影响可以忽略,而对瞬态特性的影响必须以闭环系统进行分析。对于F反馈系数及以上开环系统构成的闭环系统,开环系统的偶对将变成闭环系统的偶对。在ω》ωa1的频率范围下,有式(5),设闭环系统在主次极点分离条件下的主极点频率为ωi=Fωu。考虑到![]() 偶对中极点ωdp相对ωt的位置由比值系数

偶对中极点ωdp相对ωt的位置由比值系数 决定,即主要由ωau与ωu的位置关系所决定,

决定,即主要由ωau与ωu的位置关系所决定,![]() 则有式(6)。

则有式(6)。

阶跃响应可通过拉氏反变换得到:

![]() 瞬态特性的理论分析表明,闭环偶对的相对位置关系近似保持原有开环下的性质不变。在高频极点的影响下,闭环主极点带宽下降为ωt/α。根据以上的分析结果,得到GBCA电路设计步骤如下:

瞬态特性的理论分析表明,闭环偶对的相对位置关系近似保持原有开环下的性质不变。在高频极点的影响下,闭环主极点带宽下降为ωt/α。根据以上的分析结果,得到GBCA电路设计步骤如下:

1)设计主运放。增益带宽积由建立时间要求确定,相位裕度高于70度;

2)找出主运放的共源共栅(cascode)管的栅电容,作为辅助运放的负载电容;

3)设计辅助运放。增益带宽积(GBW)略大于主运放的GBW,相位裕度高于80度。

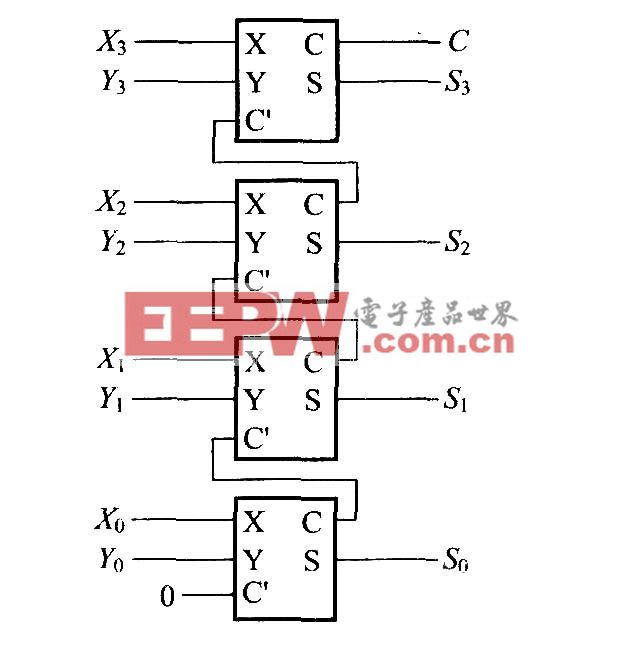

1.3 共模反馈与偏置

共模反馈电路是全差分运放的一个不可或缺的部分。本文的主运放选用动态开关电容共模反馈,如图2所示。选用这种结构的原因,一方面是这种共模反馈电路可节省功耗;另一方面是其共模电压取样电路不会限制运放的输出摆幅。尽管其具有上述优点,但它不适合两个辅助运放。因为两个辅助运放的输出负载是主运放中共源共栅管的栅电容,它们都较小。若采用开关电容共模反馈,共模反馈电路的电容势必更小,致使开关的电荷注入效应影响到电路的精度。此外,两个辅助运放也是全差分的,也需要共模反馈。由于辅助运放不需要大的输出摆幅,而且辅助运放nbooster和pbooster是接成跟随器的形式,所以稳定了输入共模也就稳定了输出共模。

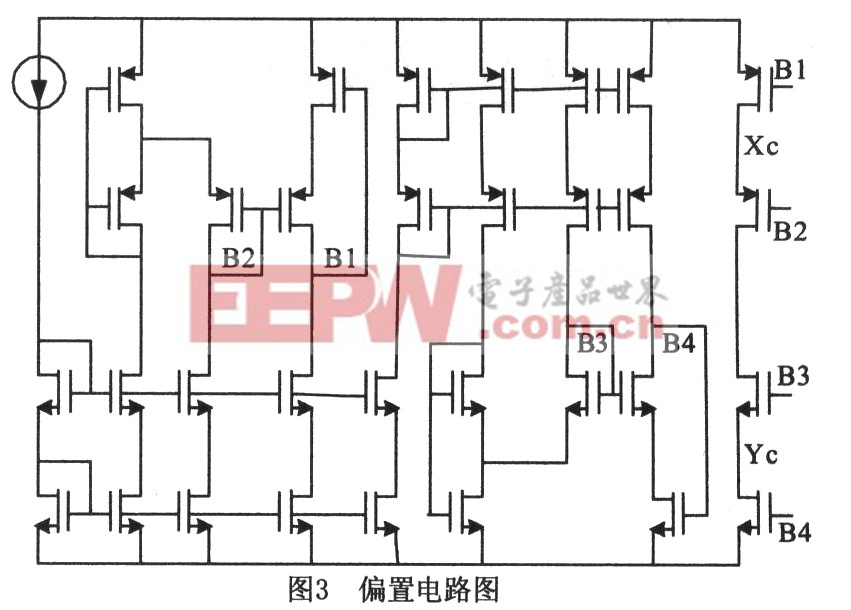

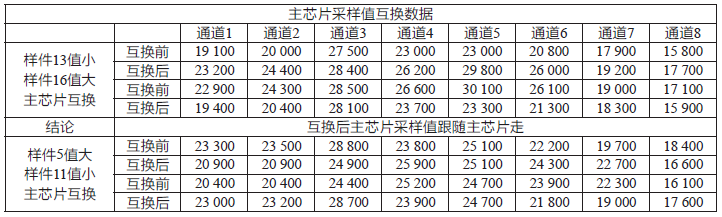

该运算放大器的主放大器和增益增强放大器使用了同一个偏置电路,偏置电路中采用了高摆幅的共源共栅电流源,如图3所示。

评论