STM32F1 0x在应用中编程的实现方法

Cortex-M3是首款基于ARMv7-M体系结构的32位标准处理器,RISC结构,包含高效灵活的Thumb-2指令集,拥有杰出的低功耗特性,为微控制器系统、汽车车身控制系统、工业控制系统和无线网络等嵌入式应用量身设计。ST公司推出基于Cortex-M3内核的STM32系列处理器,凭借其出众的性能、创新的外设、优越的功耗控制,得到众多工程师的青睐。

针对嵌入式应用的特点,STM32处理器提供功能强大的硬件调试接口――JTAG接口和串行接口,极大方便了设计,缩短了产品的开发周期。不仅如此,STM32处理器内嵌的闪存存储器允许在电路编程(In-Circuit Pro-gramming,ICP)和在应用中编程(In-Application Program-ming,IAP)。利用在应用中编程,仅需通过一根串口线,就可以完成产品固件的更新。本文对STM32处理器的在应用中编程进行了详细的分析,结合硬件和驱动给出了IAP的具体实现方法,稍加修改,便可应用于STM32处理器的所有系列产品。

1 STM32F10x处理器

1.1 STM32处理器特点

STM32全系列处理器具有脚对脚、外设及软件的高度兼容性。这给应用带来很好的灵活性,易于将应用升级到不同存储空间或不同封装的平台。STM32处理器的产品全系列兼容,使得项目之间的代码重用和移植很方便。

1.2 STM32处理器内存映射

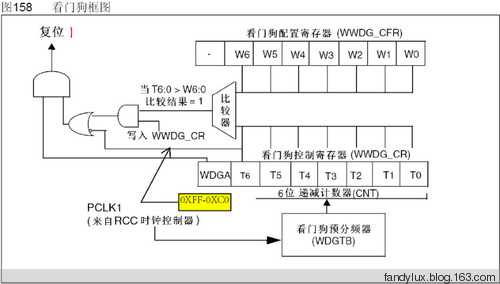

Cortex-M3的存储系统采用统一编址的方式,程序存储器、数据存储器、寄存器被组织在4 GB的线性地址空间内,以小端格式(little-endian)存放。内存映射如图1所示。

在代码区,0x00000000地址为启动区。上电以后,CPU从这个地址开始执行代码0x08000000为用户Flash的起始地址,0x1FFFF000为系统存储器(system memory)的起始地址。对于STM32处理器,可以通过配置BOOT0和BOOT1两个引脚来选择不同的启动模式,如表1所列。CPU在时钟信号的第4个上升沿锁存BOOT引脚的值,根据两个引脚的值将对应的存储器物理地址映射到启动区。

系统存储器也称为“大信息块”,有2 KB的容量。所有上市的STM32处理器,在出厂前已经烧写进去自举模式下的启动程序(Bootloader),并且将之锁定防止用户擦写。通过配置BOOT0和BOOT1选择系统存储器启动,相应的启动程序在复位后得以执行,配合PC端的通信软件,通过USART1口允许用户将程序烧写到用户Flash区。之后,将BOOT0和B00T1重新配置为用户Flash存储器启动,进入正常的应用程序。

上述的自举模式类似于ISP编程,相比其他烧写方式方便许多,但真正方便灵活的是在应用中编程(IAP),只需一根串口线就可以载入程序,复位后立即执行新的应用程序。

2 IAP功能原理

在应用中编程(IAP)使得用户可以在程序运行时重新对Flash进行编程。简单地说,IAP的编程工作是:下载编译好的二进制文件数据到RAM;将数据重新编程到特定的Flash区。这两个工作是由IAP驱动程序完成的。使用IAP功能后,系统的固件由2部分组成:第1部分是IAP驱动,不执行通常的功能,而是通过微控制器支持的任一种通信管道(如USB、USART、SPI等,本文使用USART)接收数据,并执行对第2部分代码的更新;第2部分是真正的应用程序代码,实现具体的功能。这两部分代码共同烧写在Flash中。要注意的是,这两部分代码不能重叠,否则无法实现IAP功能。

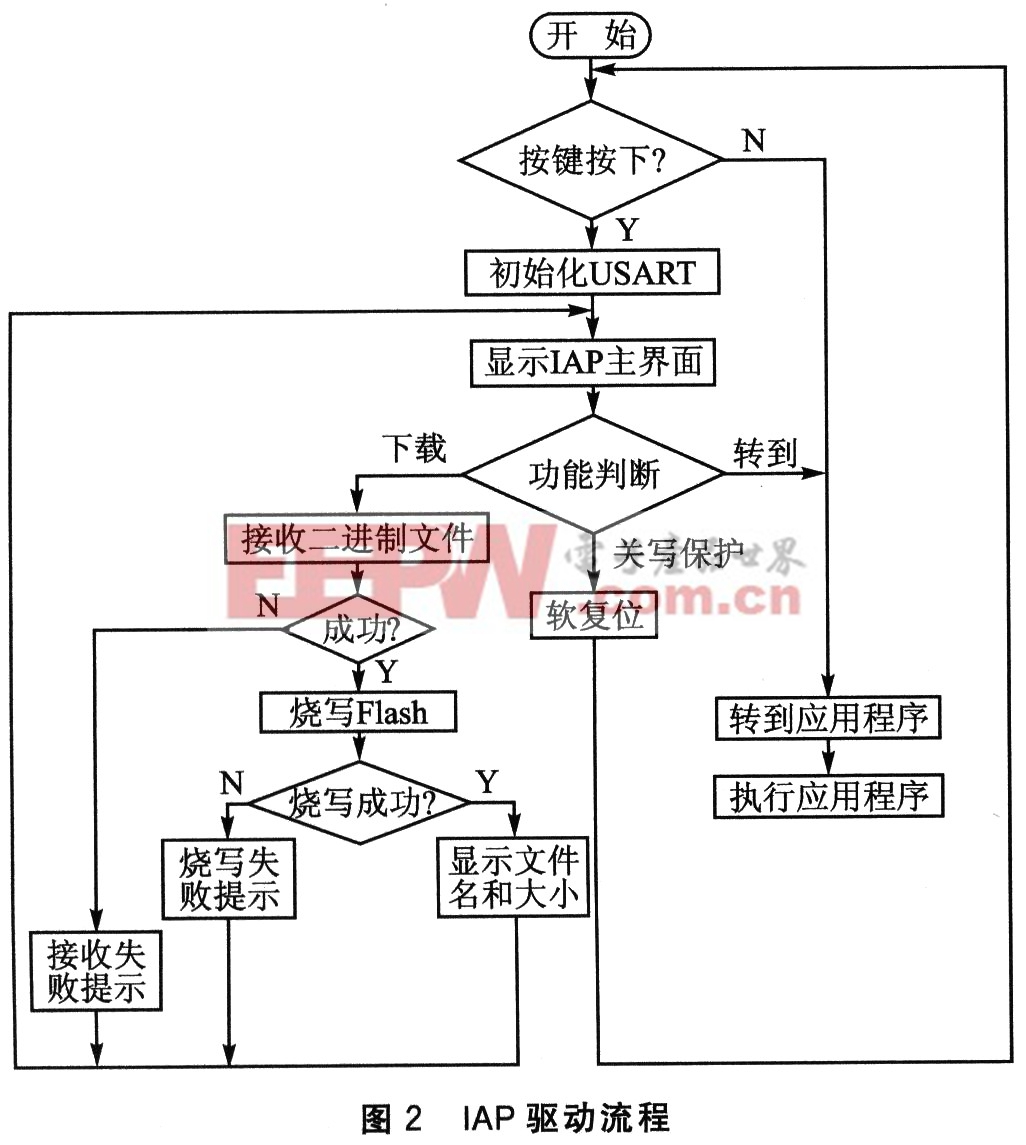

系统上电以后,IAP驱动首先运行,它主要执行如下的操作:

①根据硬件信号或软件条件判断是否需要对第2部分代码进行更新;

②如果不需要更新,则跳转到④;

③执行更新操作;

④跳转到第2部分代码执行。

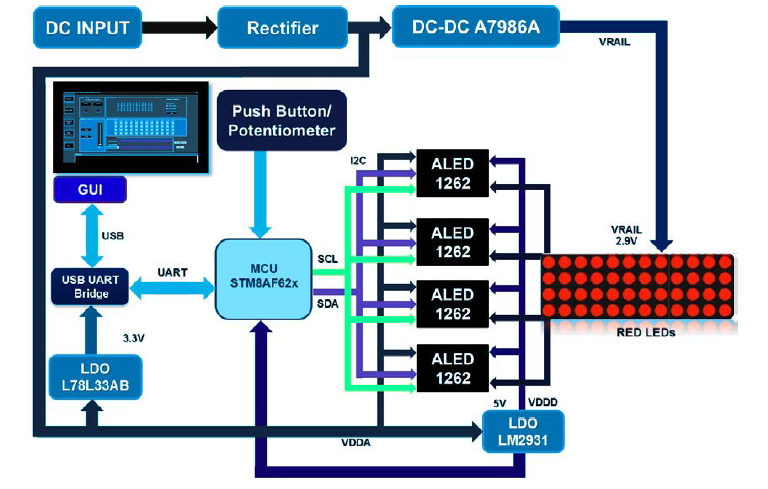

STM3210x处理器IAP驱动的流程如图2所示。图中显示IAP主界面是利用超级终端实现的,传输协议用的是Ymodem协议。需要注意的是,由于IAP驱动占用了用户Flash区的一段起始空间,因此Flash的可编程最大空间要把这部分除去。

3 IAP功能实现

3.1 硬件电路

采用STM32F10x型处理器作为核心。该处理器可全速工作在72 MHz,拥有3个USART接口,内嵌128 KB Flash和20 KB SRAM。Flash是以页的形式组织的,擦除1页的时间约为20~40 ms;在整个工作范围内其擦除次数可达10 000次,经10 000次擦除后,在+55℃的保存环境中数据保存期限仍可达20年。用户完全不必担心使用了IAP功能后对产品造成不良影响。

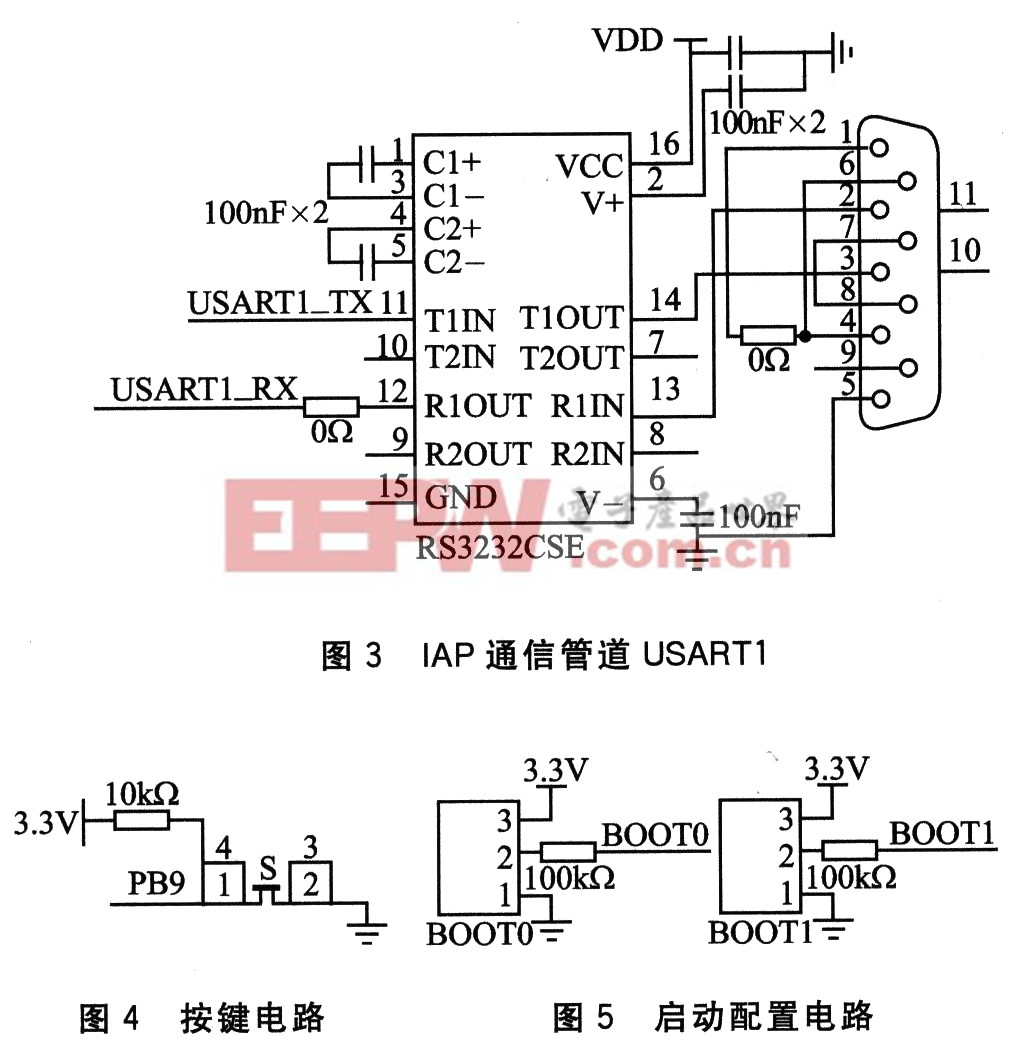

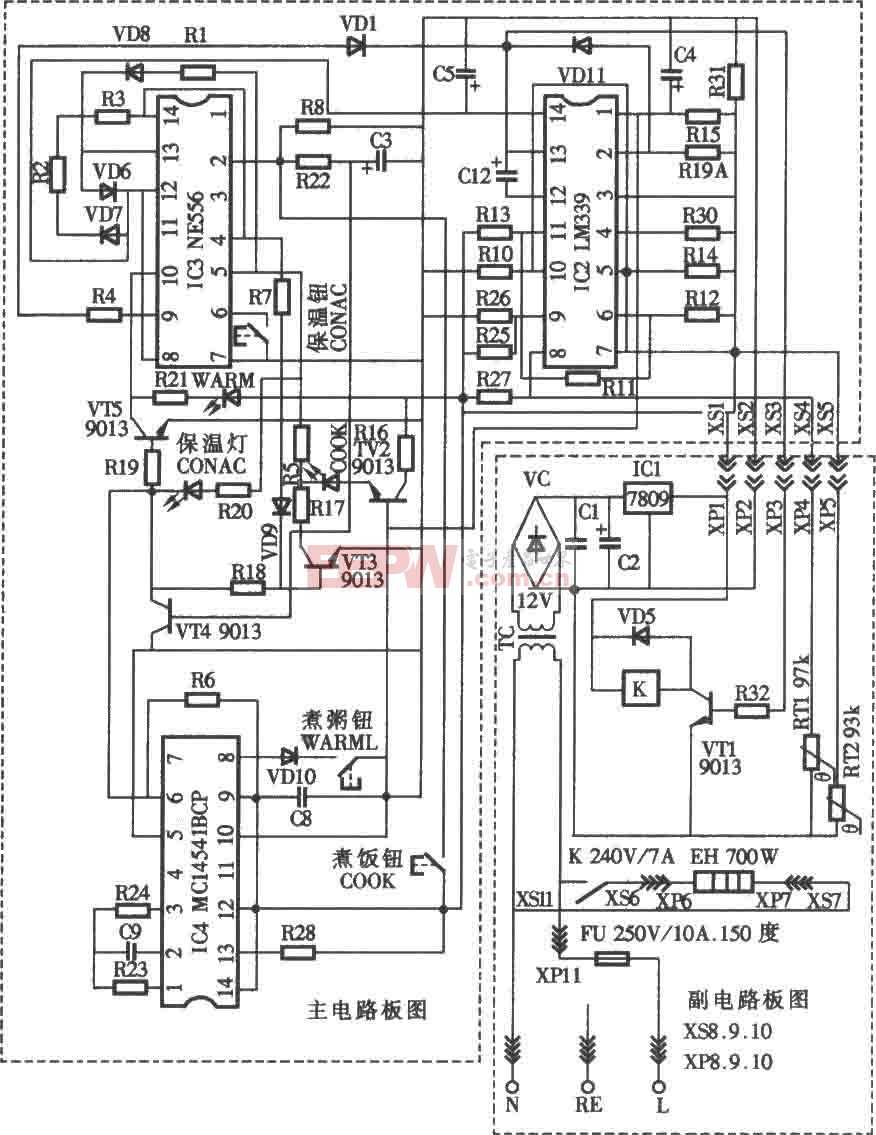

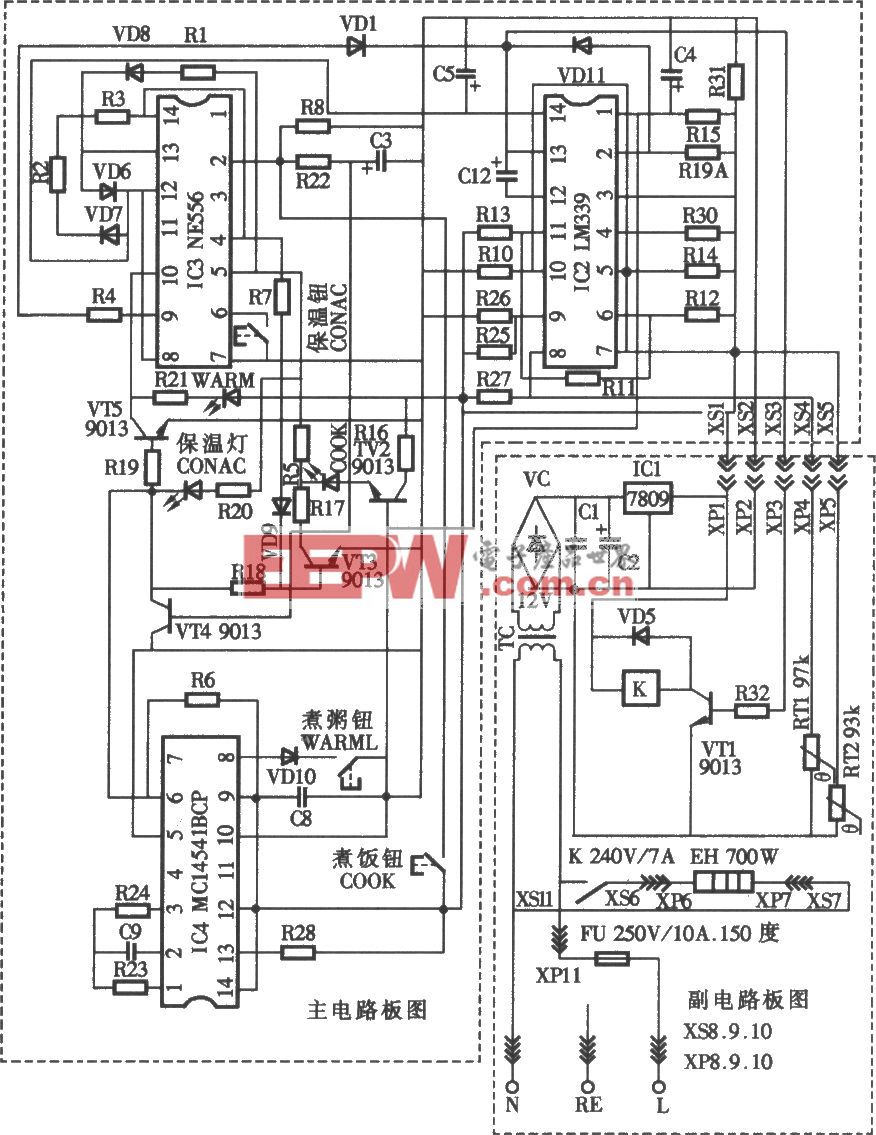

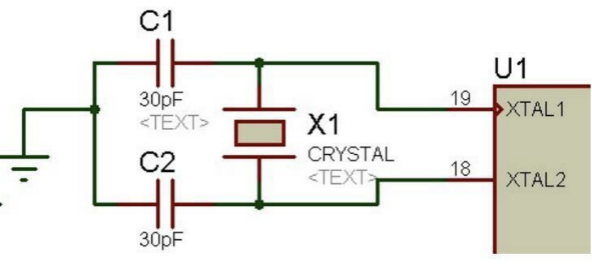

IAP驱动使用USART1口作为通信管道,PB口的第9引脚作为IAP判断是否进入IAP功能的信号线。引出一个按键,作为IAP功能选择按键,只要在上电或复位时按住此键就会进入IAP功能主界面,否则直接执行正常应用程序。BOOT0和BOOT1是启动配置跳线。相应的硬件电路分别如图3、图4和图5所示。

存储器相关文章:存储器原理

评论