12位串行A/D转换器的原理及应用开发

MAXl224/MAXl225系列12位模/数转换器(ADC)具有低功耗、高速、串行输出等特点,其采样速率最高可达1.5Ms/s,在+2.7V至+3.6V的单电源下工作,需要1个外部基准源;可进行真差分输入,较单端输入可提供更好的噪声抑制、失真改善及更宽的动态范围;同时,具有标准SPITM/QSPITM/MI-CROWWIRETM接口提供转换所需的时钟信号,可以方便地与标准数字信号处理器(DSP)的同步串行接口连接。

MAX1224/MAX1225的主要特点如下:

●1.5Ms/s采样速率;

●功耗仅18mW(典型值);

●关断电流仅1μA(最大值);

●高速、SPI兼容、3线串行接口;

●525kHz输入频率下69dB的S/(N+D);

●内部真差分采样,保持(T/H);

●外部基准源;

●无流水线延迟。

2 封装及引脚功能

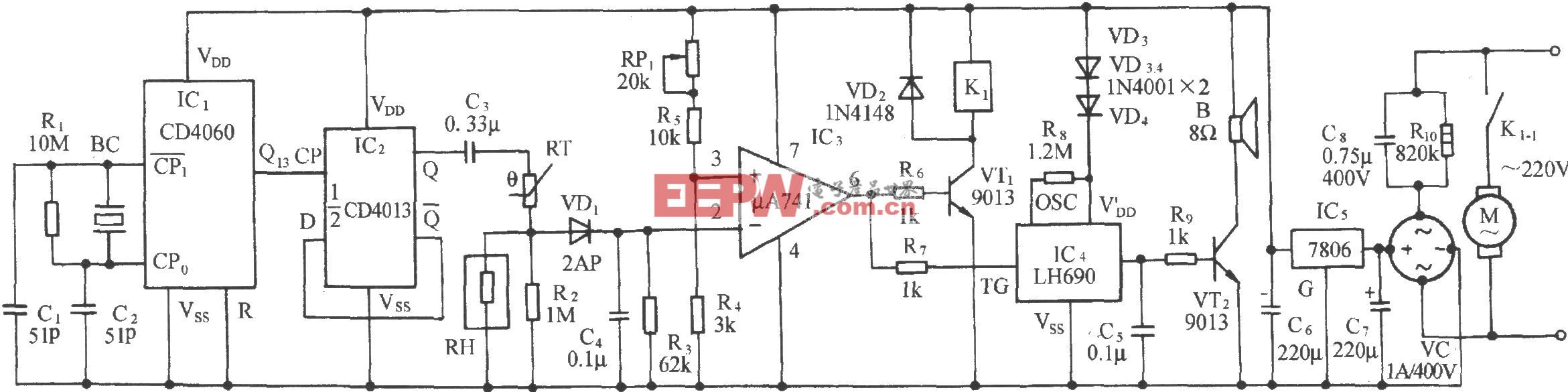

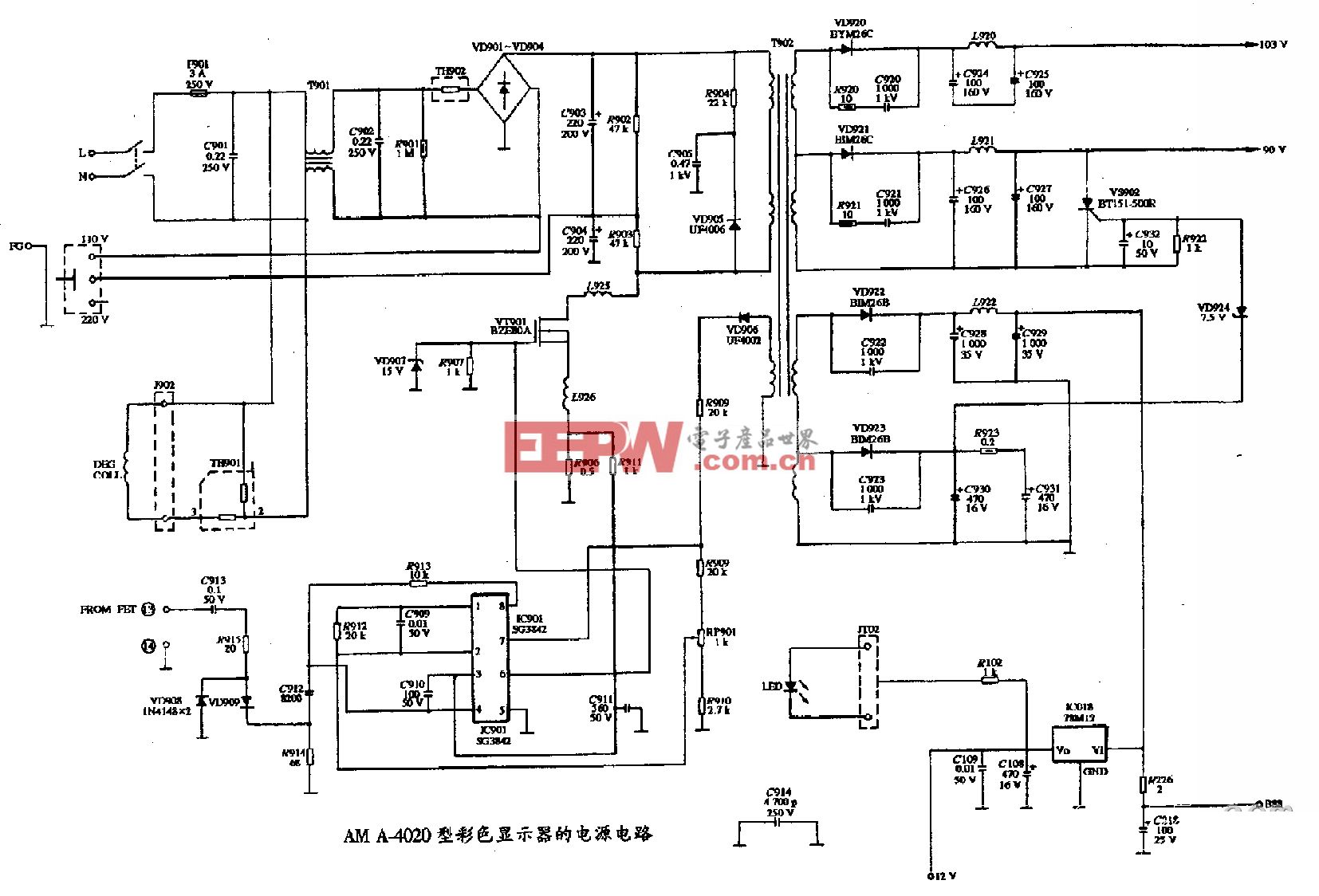

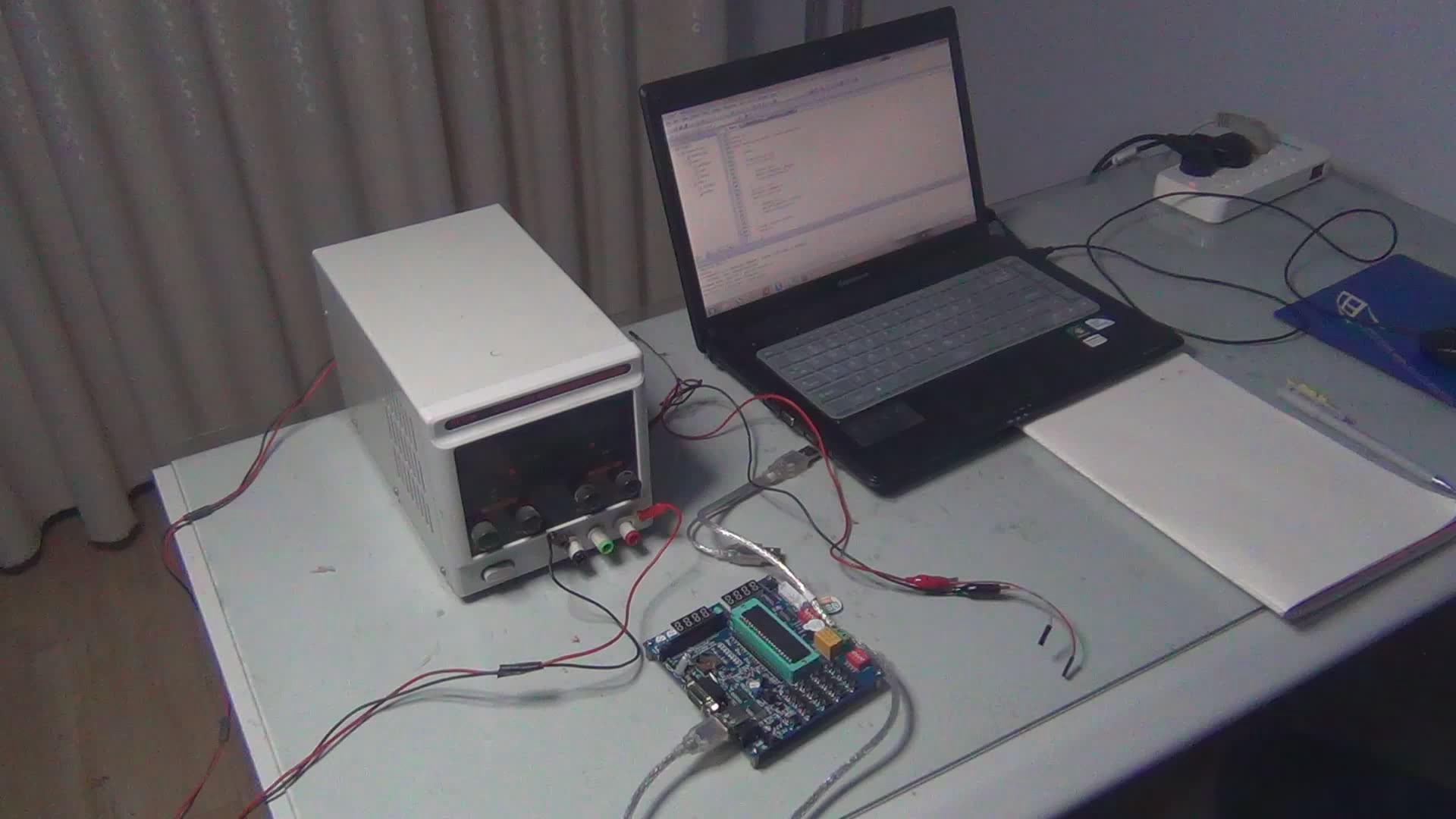

MAXl224/MAXl225采用小巧的12引脚TQFN封装,其引脚排列如图1所示。各个引脚的功能如表l所示。

3 内部结构及工作原理

MAX1224/MAX1225采用输入采样,保持和逐次逼近寄存器(SAR)电路,将模拟输入信号转换为12位数字输出信号。串行接口仅需要3条连接线(SCLK、CNVST和DOUT),提供了与微处理器(μP)和DSP的便利连接。图2给出简化的MAX1224/MAX1225内部结构。

3.1真差分模拟输入采样/保持器

MAXl224/MAXl225的输入结构由采样/保持器、比较器及开关型数,模转换器(DAC)构成。在上次转换的第14个SCLK上升沿,采样,保持器进入其采样模式。一旦上电,采样/保持器就立即进入其采样模式。输入电容器正极连接至AIN+,输入电容器负极与AIN-相连。在CNVST的下降沿采样/保持器进入保持状态,转换正负输入之间采样的差值。采样/保持器采集输入信号所需的时间取决于其输入电容器的充电速度。如果输入信号源的阻抗较高,那么采样时间会延长。

3.2输入带宽

ADC的输入采样电路具有15MHz的小信号带宽,使其能够数字化高速瞬变信号,以及通过使用欠采样技术测量带宽超过ADC采样速率的周期信号。为了避免高频干扰信号进入有用的频段,建议采用抗混叠滤波器。

3.3上电初始化与启动转换

在初始上电后,MAX1224/MAX1225要求1个完整的转换周期,以初始化内部校准电路。完成初始化转换之后,准备好正常工作。仅在硬件上电后,需要进行初始化,而在退出局部关断模式或者完全关断模式之后并不需要。CNVST拉低将启动1次转换。在CNVST信号的下降沿,采样/保持器进入其保持模式,启动转换过程。SCLK提供转换时钟,数据随后从DOUT串行移出。

3.4时序与控制

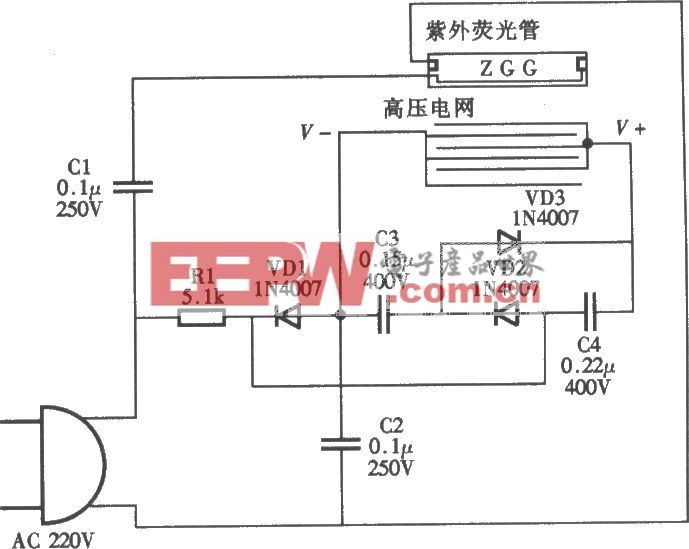

启动转换和读数据操作由CNVST和SCLK端的数字输入信号控制。图3示出时序关系,描述串行接口的工作方式。

CNVST的下降沿启动1次转换时序:采样,保持器保持输入电平,ADC开始转换,DOUT从高阻态变为逻辑低电平。SCLK用于驱动转换进程,并串行输出每个转换完成的数据位。

在第4个SCLK上升沿之后,SCLK开始移出数据。在每个SCLK上升沿的tDOUT之后,DOUT输出才有效,并且在下1个上升沿之后,还将保持4ns(tp-HOL

3.5局部关断模式和完全关断模式

将MAX1224/MAX1225设置为局部关断模式或者完全关断模式,会显著降低器件的功耗。局部关断模式尤其适合于数据采样次数少且要求快速唤醒的应用。完全关断模式适合于数据采样次数少和要求极低电源电流的应用。在局部,完全关断模式下,应保持SCIK信号逻辑低电平或者逻辑高电平,以尽可能降低功耗。

4 典型应用电路

4.1 设计原理

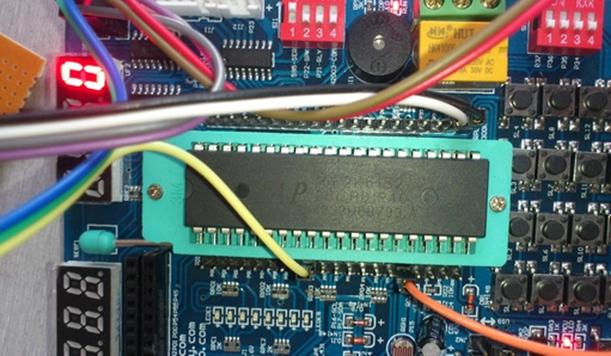

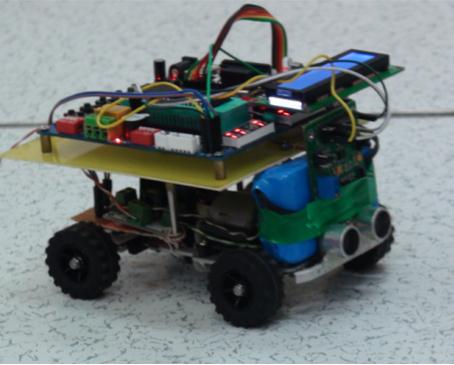

在测控系统中经常要用到A/D转换器。当被检测的模拟量是温度和压力等低速采样而需要控制的引脚又比较多时,采用并行ADC并不是最适合、最经济的方案。由于单片机往往要控制比较多的I/O口,因此使用并行ADC会限制系统I/O口功能的扩展,这时采用串行ADC比较适合。另外,由于是便携式测量仪器,所以要求功耗较低;为了减少硬件设计,多路采集信号都经过同一个ADC进行信号转换。

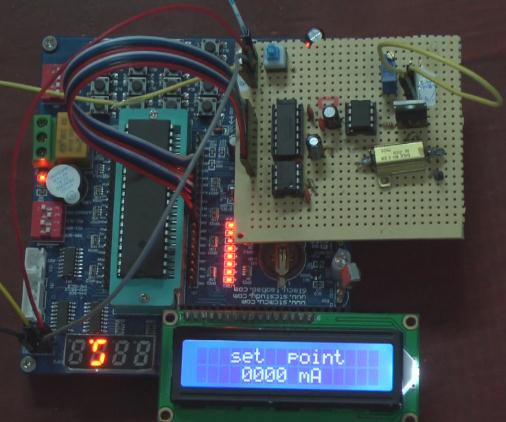

根据以上要求,笔者在温度显示仪的设计中以AT89C51型单片机为核心,采用MAX1224型12位串行A/D转换器构成采样模块进行电路设计。温度显示仪的主要功能是完成实时温度循环显示功能,它主要用于工业现场中的加热炉及具有较高温度的场合,它的测温范围是O℃~1200℃,误差要求小于

评论