一种低功耗高速的跟随器设计和实现

2.1 功耗分析

该跟随器供电电源为2.8 V,系统要求跟随器的静态功耗不超过40 μA。在典型的转角下,跟随器的功耗分析如表1所示。本文引用地址:http://www.amcfsurvey.com/article/188265.htm

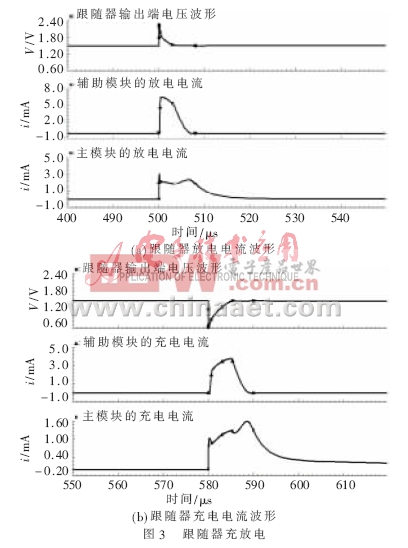

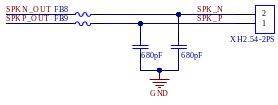

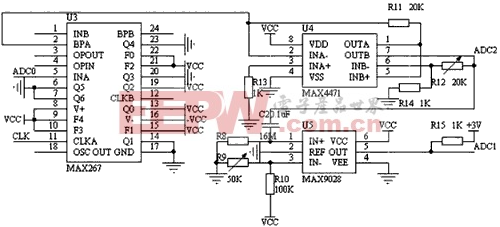

在屏幕负载电容(约20 nF)的另一端加上模拟的列信号,跟随器的充放电情况如图3所示。

辅助放电运放的电流峰值为5.7 mA,主运放的放电电流峰值为1.9 mA。辅助充电的电流峰值为3.7 mA,主运放的充电电流峰值为1.5 mA。可见辅助运放的充放电电流较大,能使充放电时间明显改善。测试与仿真表明,采用充放电模块后,像素电容上的充放电时间可缩短5~6 μs。

2.2 瞬态分析

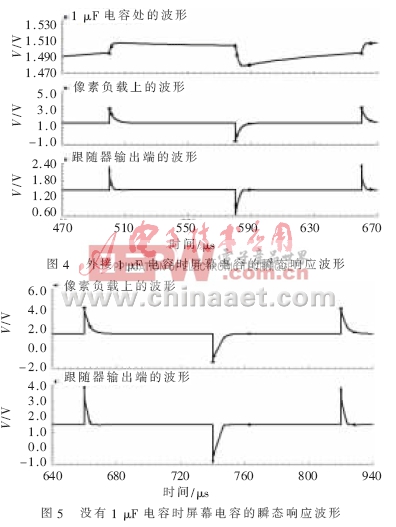

下面分析2种不同负载电容情况下,跟随器的瞬态响应情况。系统要求跟随器的充放电能力相对称,在屏幕上的充放电小于15 μs。

(1)外接片外1 μF大电容时,屏幕电容上的瞬态响应波形如图4所示,屏幕上的充放电时间为10 μs。由于外接电容与屏幕电容进行电荷分享,故外接电容对屏幕电容的充放电有改善作用。

(2)去掉片外1 μF电容时,屏幕电容上的充放电时间为13 μs,瞬态响应波形如图5所示。因此,本设计利用芯片内有限的面积,在输出端尽可能增加稳压电容。

由上可见,该高速跟随器在2种不同负载电容的情况下均能满足系统要求。在实际应用中,可考虑去掉1 μF的片外电容,从而节省芯片成本和FPC面积。本设计中,CSTN-LCD系统要求跟随器面积为600 μm×100 μm。

低功耗、高速跟随器的设计一直是制约LCD驱动芯片中的瓶颈。本文通过采用辅助充放电运放的方案,设计出一种低功耗、高速的跟随器,也有利于进一步优化芯片面积与成本,因此具有广阔的应用前景。

评论