基于MC9S08JS16和AES的USB Key设计

随着互联网与电子商务的发展,网络信息安全问题显得尤为重要。数据保密变换或信息加密,成为对计算机信息进行保护的最实用和最可靠的方法。各种加密技术如软件自校验、密码加密、钥匙盘等软加密技术和扩展卡、并行口软件加密狗等硬加密技术应运而生,而USB接口密钥(USB Key)凭借其独特的优势和极高的安全性备受青睐。

USB Key是一种通过USB(通用串行总线)接口直接与计算机相连、具有密码验证功能、可靠高速的小型存储设备。USB Key的设计小巧精致、携带方便。由于是USB接口设备,USB Key通过USB端口提供的电源来工作,不需要额外的电源。USB Key自身所具备的存储器用于存储一些个人信息或证书,USB Key的内部密码算法可以为数据传输提供安全的管道,适用于单机或网络应用的安全防护产品。

1 系统工作原理及硬件设计

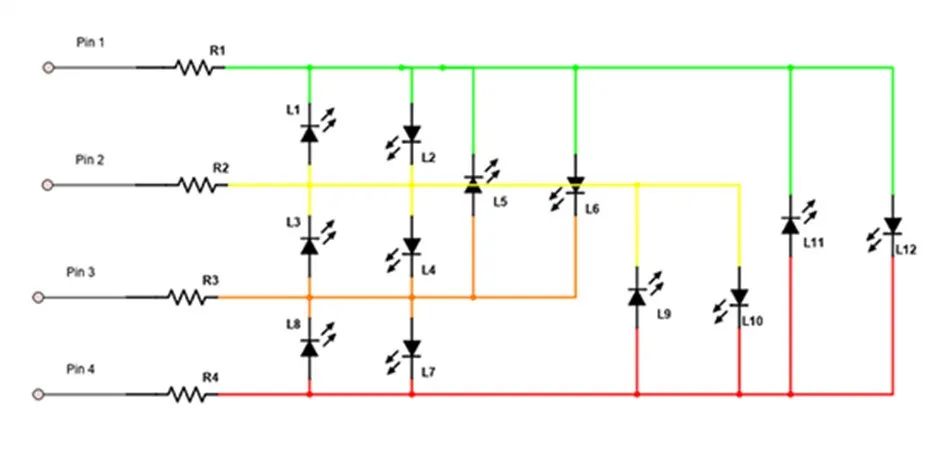

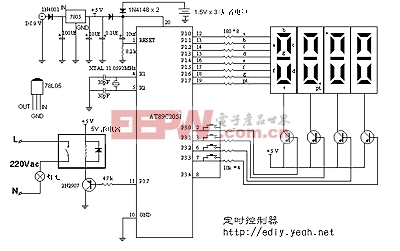

USB Key(简称Ukey)通过USB接口与PC机相连,用户可以通过位于PC机的客户端向Ukey发出命令,Ukey通过内部固件中算法实现数据加密,然后将加密后的数据返回客户端。其工作原理如图1所示。设计选用了8位USB微控制器(MCU)MC9S08JS16,MC9S08JS16型MCU内置全速USB2.0控制器并集成了1个USB收发器,同时含有高达16 KB的Flash和512 B的RAM。

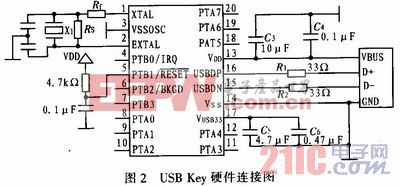

用户可以通过片内专用的3.3 V稳压器或VUSB3.3引脚外接3.3 V电源为USB收发器和上拉电阻提供电源,这里采用片内的3.3 V稳压器为USB收发器提供电源(须使能USBCTL0寄存器的USBVREN位),硬件连接图如图2所示。

USB模块需要两个时钟源,分别为24 MHz总线时钟和48 MHz参考时钟。48 MHz时钟源由MCGOUT直接产生,为了获得48MHz时钟速率,MCG(通用时钟产生器)必须被适当配置为PLL使能的外部占用模式PEE(PLL EngagedExternal),外接一晶振。MC9S08JS16的USB模块选择内部上拉电阻(使能USBCTL0寄存器USBPU位)USB主机通过检测上拉电阻检测USB设备的联结并确定设备速度。

2 系统软件设计

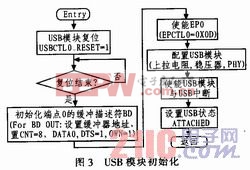

2.1 USB设备初始化

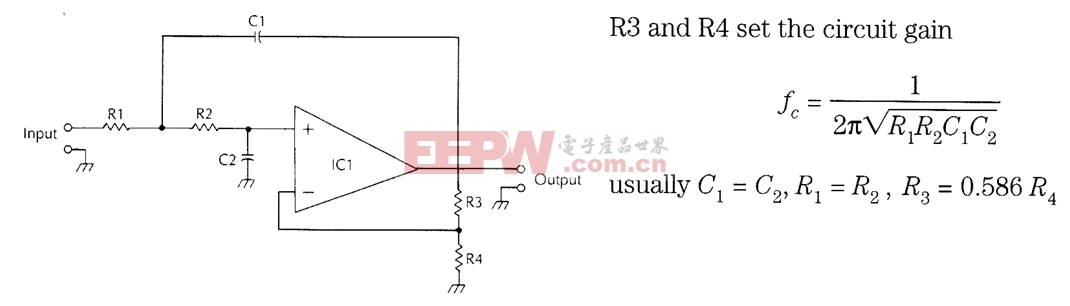

图3为USB模块初始化流程图,固件代码初始化USB模块,使其准备联结到USB主机。通过设置USBCTL0寄存器的RESET位,重置USB模块和所有寄存器为默认状态,完成对USB RAM,BD(buffer descriptor)寄存器的初始化,特别是对于端点0的BD,设置EPAD寄存器,指示端点寄存器在USB RAM中的存储,为了接收DATA0数据包,状态与控制寄存器设置为(DTS=1,OWN=1,DATAO/1=0)。使能端点0,并根据硬件设计配置USB模块,使能上拉电阻,3.3 V稳压器与PHY。开放USB模块和USB中断,设备被置为连接状态。

2.2 AES加密算法

系统采用128位高级加密标准AES(Riindael)算法进行数据加密。AES(Advanced Encxyption Standard)是美国国家标准与技术研究所用于加密电子数据的规范,用于代替现有的DES算法,AES作为新一代的数据加密标准汇聚了强安全性、高性能、高效率、易用和灵活等优点,被预期能成为公认的加密包括金融、电信和政府数字信息的方法。

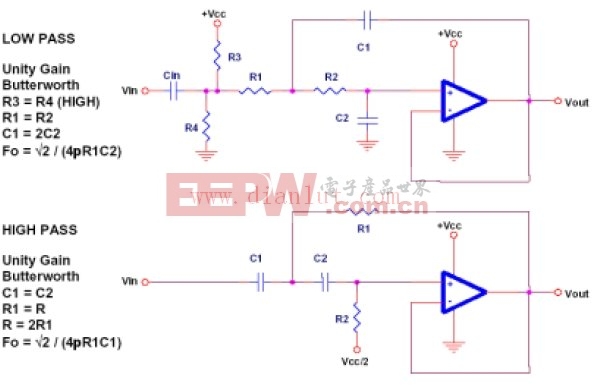

AES算法是基于置换和代替的。置换是数据的重新排列,而代替是用一个单元数据替换另一个。AES加密例程开始是拷贝16字节的输入数组到一个名为State(态)的4x4字节矩阵中。AES算法加密过程如图4所示。

评论