基于DP标准发射端扩频时钟发生器电路设计

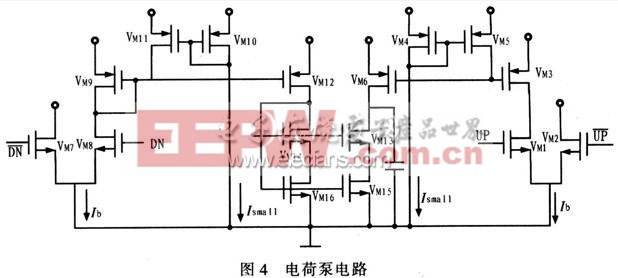

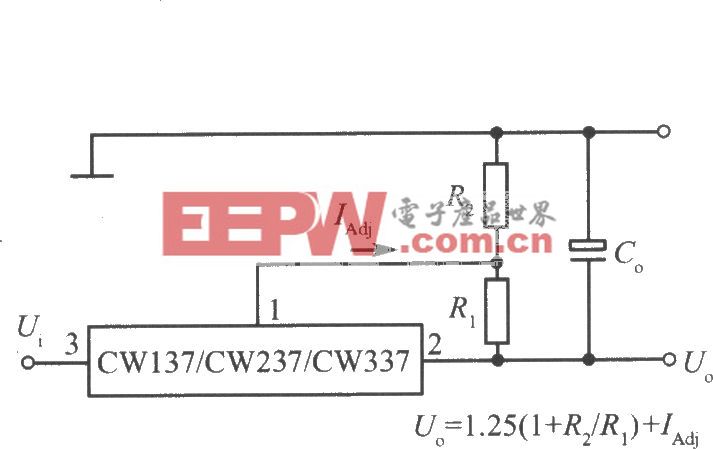

电荷泵锁相环具有低功耗、高速、低抖动和低成本等特点,广泛应用于无线电通信、频率综合器、时钟恢复电路中。电荷泵电路在锁相环路(PLL)中起着非常重要的作用,其主要功能是把鉴频鉴相器(PFD)的数字信号UP和DOWN转换为模拟信号,从而控制压控振荡器(VCO)的频率。当PFD给出高精度的相位误差时,电荷泵对整个环路的性能起决定性作用。当PLL锁定在某个频率时,电荷泵电路的输出必须保持在一个常数。因此,在设计电荷泵电路时,产生一个稳定步长的电压是很重要的。实际的电荷泵不可避免的存在电荷泄漏、充放电流失配、泵开关时间延时不同等不利因素,这些因素都不同程度地造成输出频率的相位偏差,进而降低输出时钟的抗噪声性能。该系统设计采用差分电路结构,此结构具有以下优点:消除了跳跃现象;可以丁作在较高频率,满足整个PLL的设计要求;由于对称性,不易产生偏差;减小电源、地及衬底噪声的影响;NMOS与PMOS开关特性不匹配对整个性质将不再起决定性作用,原来要求NMOS与PMOS相匹配的地方,现在只需NMOS或PMOS自身相匹配即可。该电荷泵电路如图4所示,它由大摆幅电流镜及由上拉泵和下拉泵电路所构成的对称电荷泵所组成,属于全差分型电荷泵电路。上拉泵和下拉泵均由差分输入对V M1和VM2,电流镜VM3,偏置电流源Ib和ISMALL,以及弱上拉电流镜VM4和VM5所组成。该电路是一种新的全差分电荷泵结构,与传统电荷泵电路相比,该电路具有输出范围宽和无跳跃现象等优点,同时还可以有效地解决电荷泄漏和充放电失配等问题。

3.4 调制电荷泵电路

采用调制电荷泵三角波调制压控振荡器的控制电压以达到扩频的效果。文献[5]中给出了调制电荷泵的参数:调制电流为2.33μA,调制频率为30 kHz。电荷泵的输出都是采用单管,而不是更有利于抑制失配度的级联管,原因在于级联管限制了电荷泵的电压输出范围,压控振荡器在1.15~2.43 V线性范围内不是所有情况下都能处于饱和区工作。该设计通过增加管子的栅长L,即增加从管子漏端看进去的电阻来减小失配度,而管子增大所引起的时钟馈通及电流泄露等问题比电流失配对系统的影响小。

3.5 滤波器电路

环路滤波器(LPF)连接在电荷泵和压控振荡器之间,它决定锁相环的基本频率特性。实际上,正是由于环路滤波器的存在,锁相环才可以选择工作在任意中心频率和带宽内。环路滤波器可以采用无源滤波器或有源滤波器。该设计采用无源低通滤波器,用基于锁相环交流频域特性分析的方法。在该滤波器的设计中,如果锁相环带宽、相位裕度和零极点选择合理,只需经过1~2次试算,就可以得到正确结果。这种设计方法的优点是直接以锁相环的交流特性为出发点,利用使系统稳定的简单条件,就可以设计出环路滤波器。这为低相位抖动、快速锁定锁相环的行为级设计提供了一种快速准确的途径。

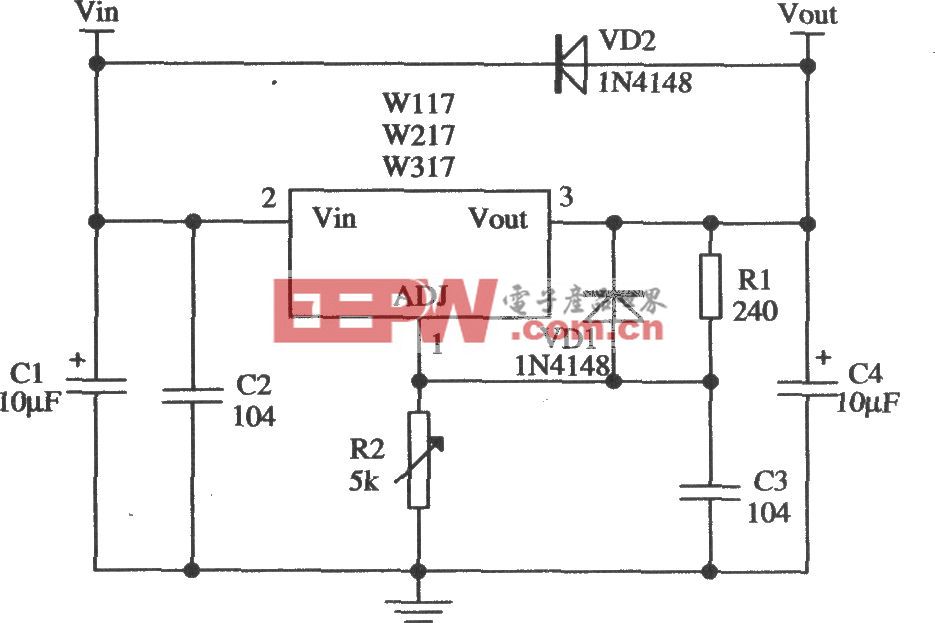

3.6 压控调节器电路

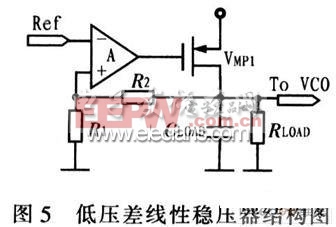

考虑到压控振荡器易受到电源噪声的影响,而压控振荡器的性能是整个锁相环系统的关键,所以为压控振荡器提供1个稳定的电源电压是非常必要的。本文采用折叠式共源共栅结构,如图5所示。

图5中,补偿电容为4.7 μF,基准点电压Ref来自带隙基准,输出电压由反馈电阻和运放增益决定:

为了减小输出电压的误差,需要设计增益较大的运放,考虑到环路的稳定性及环路建立时间,把补偿电容的极点作为整个环路的主极点,这就要求运放具有较高的带宽。

用负载电阻模拟压控振荡器,取Rload为150~500 Ω,输出5.2~18.8 mA电流来提供压控振荡器的电流,这一输出范围对运放的电压输出范嗣提出严峻要求。为了提高输出电压的电源抑制,可以设计输出管VMP1工作在饱和区,但这就降低了低压差线性稳压器的效率(近似为输出电压与电源电压的比值);另外也可通过增加VMP1,管的栅长来提高电源抑制,但这样就使得运放的主极点减小,整个环路稳定性变差。低压差线性稳压器的设计还需综合考虑电荷泵输出电压,压控振荡器线性工作范围等因素。

评论