SAR ADC驱动运算放大器的选择

运算放大器输出级极限

运算放大器的轨至轨运行是指其输入级或输出级,或者是指其输入级与输出级。作为驱动 SAR ADC输入端的一个缓冲器,我们更关注运算放大器轨至轨的输出能力。一般说来,该输出能力表明了输出级能够接近电源轨的程度。

通常情况下,当信号振幅增大时,低频信号 (1kHz)、总谐波失真保持不变。只有当输出电压和电源轨之间的差值低于 10mV 时,才会导致性能显著下降。而当输出信号频率增加时,输出电压和电源电压之间的差值也会随之增大。对于 10kHz 的信号而言,当上述电压差值低于 200mV时,相关性能才开始下降;对于 20kHz 的信号而言,当上述电压差值低于 300mV 时,相关性能才开始下降;以此类推。考虑到运算放大器的输出级极限,这些测量结果将有助于确定 SAR ADC 电路的最佳工作点。

RC 负载对运算放大器的影响

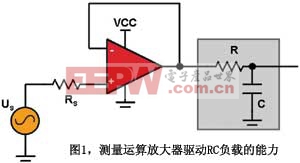

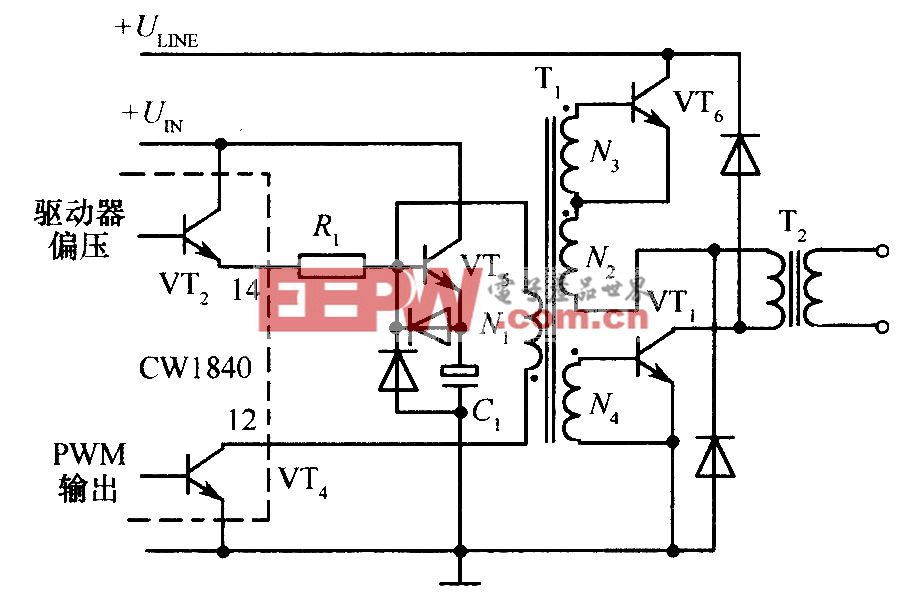

对于最佳的 AC 性能,运算放大器的输出信号摆幅介于 450mV ~ 4.55V 之间。用于驱动 SAR ADC 运算放大器的第二个重要参数就是要找出其驱动不同的 RC 负载的极限。推荐在 ADC 输入端采用 RC 滤波器限制输入噪声的带宽,并帮助运算放大器驱动由 SAR ADC 产生的开关电容负载。图 1 示出了测试调整电路帮助确定具有 RC 负载的运算放大器的驱动极限。

首先,将RC电路的截止频率定为1.5MHz。这一频率限额是以在未来设计中将要采用的ADC预期采集时间为基础设定的。另外,如欲保持截止频率不变,则应采用不同 RC 组合和不同信号频率的测量工作。对于较低的频率而言,使用较小阻值的电阻或较大容量的电容器。当信号频率增大时,阻值较大的电阻应与容量较小的电容器配合使用,以保持相关性能的稳定。

ADC 输入的非线性特性

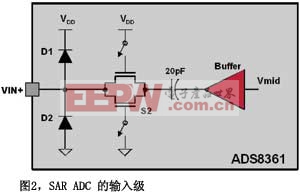

减小输出电压摆幅将有助于保持运算放大器的性能,但还应考虑信号的完整性及其对不同系统组件的影响,随后可向ADC输入端发送一个信号。图2为常见的SAR ADC 输入级。在流经输入静电放电 (ESD) 保护二极管之后,则可对一个采样电容器和两个场效应晶体管 (FET) 开关中的信号进行采样。如果采用了理想的组件,本设计不会对采样阶段的运算放大器的驱动产生任何影响。遗憾的是,这些组件并非理想的解决方案,特别是临近电源轨的等效负载非线性特性,向缓冲电路提出了新的挑战。

减小从运算放大器至ADC输入端的信号摆幅,将带来诸多益处。在运算放大器的输出端应用5VPP的信号将减弱总谐波失真(THD)。另外,在 SAR ADC的输入端应用5VPP的信号时,要求运算放大器拥有强大的驱动能力。以2.5V的偏移量,将信号电平从5VPP减小到4.1VPP,将同时为正、负电源轨增加450mV的裕度。

另一个问题是:ADC的满量程衰减。在ADC产品说明书中,转换器的额定电源电压为5V,其额定满量程 (FSR) 为一个5VPP的信号。注意,ADC的输入FSR取决于应用参考电压,可以针对新的运行条件,对FSR进行调整。当使用的参考电压为2.5V时,对于ADS8361而言,在2.5V或5VPP时FSR 输入信号将为 ±2.5V。将参考电压调整为2.048V 后,在2.5V或4.1VPP时,新的(调整后的)FSR 输入信号将为 ±2.048V。现在,在4.1VPP的输入信号中,我们就有了一个全16位的转换功能,而无需衰减动态范围。

采集时间与吞吐率之间的关系

当选择 ADC 时,最重要的参数就是速度或吞吐率。该参数是采集(采样)时间和转换时间的组合。当转换时间的缩短超过产品说明书中规定的限额时,将严重影响 ADC 的性能。采集时间决定着为采样电容器充电的快慢,以达到规定的吞吐率。在采集时间临近结束时,输入采样开关开启,转换过程随即开始。在转换周期即将结束时,从 ADC 所获得的数据等同于转换周期开始时(或采集周期结束时)采样电容器上的电压。不论 ADC 性能多么优秀,如果没有足够的时间对采样电容器进行充分的充电,那么转换结果将会出现与实际模拟输入信号不符的情况。为了在系统设计期间控制上述参数,有两种方法可供选择:1)采用输出阻抗低、运行速度快的运算放大器,或 2)在 ADC 模拟输入端采用高截止频率的 RC 滤波器。这种方法可导致运算放大器稳定性方面的问题,同时会给输入模拟缓冲电路带来较大的噪声影响。也可以使用运行速度适中的运算放大器和较低截止频率的 RC 滤波器,延长转换器的采集时间。

优化RC实现特定的频率性能

首先,选择适合系统电源轨的运算放大器,并记录下这种放大器的输入和输出极限,同时弄清楚ADC输入范围调整的可能性,以便更好地与运算放大器的性能相匹配。其次,确定适当的采集时间,并相应地设定系统时序。然后,选择RC电路中的相关数值, 采集时间和RC滤波器时间常数之间的比率 (k) 取决于ADC的分辨率。最后,选择具备足够增益带宽的运算放大器来驱动该RC电路,而且所选的运算放大器应具有适当的调整时间。对许多不同SAR转换器的应用来说,该设计驱动电路的程序非常稳健而有效。然而,有时候作为能够改善性能系统的RC滤波器的一些优化措施而言,这仅仅是一个开始。

在优化ADS8361前端的输入RC滤波器之前,需要确定有关的工作条件:输入时钟频率为9.9968MHz,采样频率为199.936kSps;由这两个数值得到ADC转换时间为1.6ms,采样时间为3.4ms。因此,该转换器需要12个时间常数的外部RC滤波器来相应的采集时间匹配。这种条件可将RC电路的带宽设置为:

其中:k =12,由此可以实现562kHz的带宽。

低噪声系统可以采用尽可能高的带宽,但是,也不要把带宽设置得过高。因为带宽越高,其所允许的噪声也就越高,所以应在 RC 设定时间和该带宽之间取得一个平衡值。为了确定 RC 滤波器的最佳值,我们使用一个低输出阻抗的信号源。注意,最终计算结果应包括信号源的输出阻抗。在该示例中,该阻抗为 20Ω。从这些测量结果中发现,当 k = 7 时,可获得最佳 THD 值;而当 k = 6 时,可获得最佳的 SFDR 值。并且,k 值越小,RC 滤波器的带宽也就越低,从而降低了噪声。然而,当 k 值变小时,性能也随之降低。出现这种情况是因为时间常数太大,而且它不能对采样电容器上的输入电压进行相应的设置,从而导致测量误差的出现。

结论

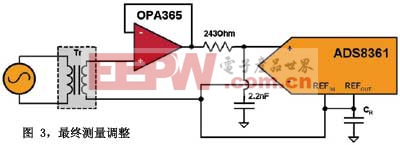

为了完成信号链的最终性能评估,选用当k = 6.36或截止频率 = 298kHz 时的RC滤波器。在这种前提下,我们采用一只2.2nF的COG型电容器和一只243Ω的电阻。

当采用ADC最高的采样速度时,采集时间为 400ns。采用上述相同标准(k = 6.36)时,一阶滤波器的有效噪声带宽为 4MHz。当采集时间由 400ns 延长至 3.4ms 时,有效噪声带宽则下降为 562kHz。图 3为最终调整图。

晶体管相关文章:晶体管工作原理

电容传感器相关文章:电容传感器原理 晶体管相关文章:晶体管原理 电子负载相关文章:电子负载原理

评论