PLL电路设计原理

在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

一 PLL电路的基本构成

PLL电路的概要

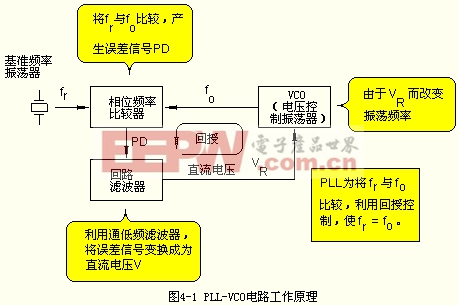

图1所示的为PLL电路的基本方块图。此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。)

利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL的构成

PLL可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

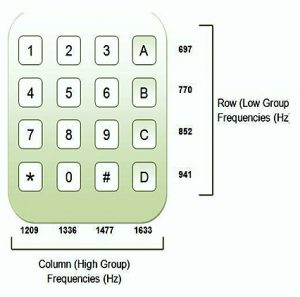

从图1的PLL基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。在此,假设基准振荡器的频率为fr,VCO的频率为fo。

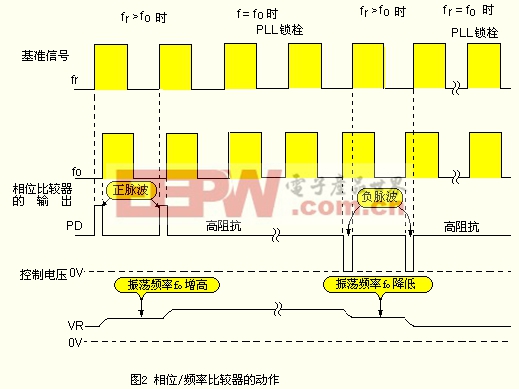

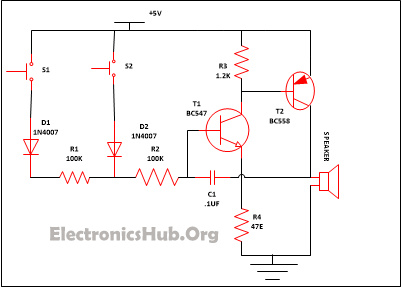

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。此时的相位比较器的输出PD会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。如果有相位差存在时,便会产生正或负的脉波输出。)

此一PD脉波信号经过回路滤波器(LoopFilter)的积分,便可以得到直流电压VR,可以控制VCO电路。

由于控制电压vr的变化,VCO振荡频率会提高。结果使得fr=f。在f与f的相位成为一致时,PD端子会成为高阻抗状态,使PLL被锁栓(Lock)。

相位比较器的工作原理

此所说明的相位比较器为相位.频率比较器(PFC:Phase-Frequency Comparator)之型式,后述之LSI MC145163P便内藏有此一电路。

此一型式的相位此较器并非只做![]() 相位的比较,也即是,并非只做之比较,在频率f不同的场合,也可以做为频率比较器工作原理。

相位的比较,也即是,并非只做之比较,在频率f不同的场合,也可以做为频率比较器工作原理。

所谓相位差利时△与时间t的关系为![]()

在只做相位检出的场合,例如,可能分辨不出是延迟300°或前进60°。可是,在相位-频率比较器中,如果frgt;fo则被视为是相位延迟。

回路滤波器的选择方法

回路滤波器的时间常数与PLL控制的良否有很大的关系。其详细的计算方法虽然不在此说明,但是,基准频率fr为l0kHz时,输往回路滤波器的脉波周期为0.1mS。

为了保持电压值VR而增大回路滤波器的时间常数时,便无法追踪VCO的振荡频率的变化。如果时间常数太小时,会在VR上出现涟波,使PLL的稳定度恶化。

因此,根据经验,回路滤波器的时间常数,选择大约为基准频率的周期(1/fr)的数百倍。在此选择约为数十mS。

评论