采用CSMC工艺的零延时缓冲器的PLL设计

1 引言

本文引用地址:http://www.amcfsurvey.com/article/186087.htm本文在传统锁相环结构的基础上进行改进,设计了一款用于多路输出时钟缓冲器中的锁相环,其主 要结构包括分频器、鉴频鉴相器(PFD)、电荷泵、环路滤波器和压控振荡器(VCO)。在鉴相器前采用预 分频结构减小时钟信号在传输过程中受杂散分布的电容电感的影响,避免产生信号畸变、漂移等严重影 响电路随时钟精确工作的现象。PFD 比较两个分频器的信号,产生误差信号对电荷泵进行充放电,电荷 泵产生的模拟信号经过环路滤波器后调节VCO 频率。VCO 输出后的分频器的分频系数与预分频系数相 等,目的是使输出与输入的时钟信号频率相同,起到缓冲而不是分频的效果。锁定后实现输入与输出信 号零延迟。

2 电路结构

2.1 鉴频鉴相器(PFD)

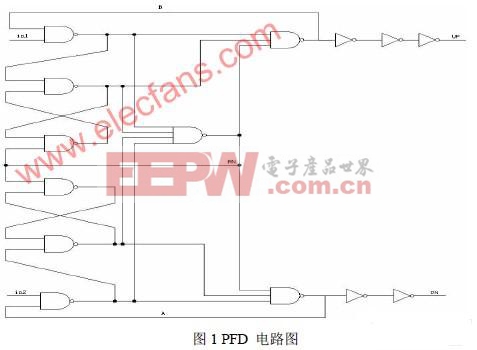

PFD 产生关于频率和相位误差的信号,其脉冲宽度与相位误差成比例的变化,传输给电荷泵及环路 滤波器引起压控振荡器控制电压的变化,进而改变振荡频率。电路工作的进程如图2 所示,这是一个下降沿比较的结构,由两个基本RS 触发器和两个带复位端的RS 触发器组成。这种鉴相器不仅可以对相位 进行比较,也可以对频率进行比较,锁存结构记忆了前一次的输入信号状态,从而决定了下一次的输出 状态。

从复位信号有效开始考虑,以参考时钟超前为例,in1 的下降沿首先使A 由高变低,接下来的in2 下降 沿也使B 由高变低,四输入与非门的四个输入端都为高,复位信号RN 变低(有效),使A 和B 在很短 的时间内变高 。下一个周期重复前一个步骤。反向器的作用是为了消除进入电荷泵的信号上的毛刺。另 外由于复位信号是由四输入与非门产生的,其本身的延时足以使复位脉冲有一定的宽度,减小鉴相死区, 又不至于太宽出现错误的输出波形。

2.2 电荷泵(CP)

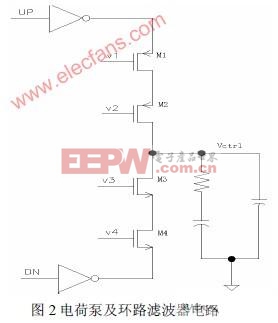

电荷泵设计的关键是降低抖动和电流失配引起的毛刺以及在开关瞬间的电荷转移。调节电荷泵的尺 寸使匹配电流、增益、电容参数得到优化。本文的电荷泵结构简单,如图2 所示,由M1M4 组成连个 共源共栅结构的恒定电流源,高的输出阻抗使其接近理想的电流源,输出电阻近似为(gm2+gmb2)ro2r01 或者 (gm3+gmb3)ro3r04。UP 和DN 信号经过反向器作为电荷泵的充放电开关,v1v4 是由基准电路产生的固定 电平,使电流源工作在饱和区,关系满足v2>v1>v3>v4。当UP 为低DN 为高时,上半部分电路导通, 通过反向器内部的电源对电容充电;反之,则下半部分导通,Vctrl 通过M3、M4 及反向器内部对地放电; 另外,由于开关不与输出直接相连,几乎不受电荷注入的影响,同时四个管子在工作都处于饱和状态可 以消除电荷分享效应。在锁定情况下,PFD 产生同样宽的基本脉冲UP 和DN,使电荷泵的灌电流和源 电流相等,这样输出的净电流为0 ,保持VCO 的控制电压不变。

由于电荷泵是个对电流匹配程度要求极高结构,因此在设计尺寸方面,要增大电流源的沟道长度, 以减小沟道长度调制效应的影响,这种结构下电荷泵电流失配率仅为2.18%。

分频器相关文章:分频器原理 电荷放大器相关文章:电荷放大器原理

评论