一种数模信号转换的实际案例介绍(三)

第6步:根据设计目标检查解决方案总噪声

本文引用地址:http://www.amcfsurvey.com/article/186058.htm充分了解所设计电路中的各种误差源是极其重要的。为了获得最佳SNR,我们需要写出前述方案的总噪声方程。方程如公式1:

我们可算出运算放大器输入端的总噪声,并确保其低于41.6 nV/rtHz,一如我们所预期的那样。方程如公式2:

为了在整个带宽上对总噪声进行积分,我们可看到在滤波器带宽上的ADC输入端的总噪声是3.05μV,低于设计所需的4.16μV。由于AD8641的转折频率低于100 Hz,故此例中的低频噪声(1/f)可忽略不计。程如公式3:

保持良好的信噪比需要关注信号路径中每一处细节的噪声,并有良好的PCB布局。避免在任何ADC下方布设数字线路,否则会将噪声耦合至芯片管芯,除非在ADC下方铺一个接地层用作屏蔽。诸如CNV或时钟之类的快速开关信号不应靠近模拟信号路径。应避免数字信号与模拟信号交叠。

公式1

公式2

公式3

第7步:运行模拟并验证

刚开始验证电路设计时,使用Pspice宏模型(可从ADI网站下载)比较合适。快速模拟显示出我们为解决方案所设计的信号带宽。图5显示了位于AD7685输入端可选RC滤波器之前和之后的响应。

如图6所示,10-kHz带宽上的总输出噪声接近31μV rms,略低于41μV rms的设计目标。在量产之前需要制作原型并验证整套解决方案。

图6 图3所示电路的噪声响应模拟

总结

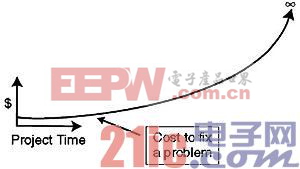

如今许多设计要求低功耗、低成本,而许多系统既负担不起最昂贵的器件,也无法承受低噪声器件的更高功耗。为了从信号调理电路得到最低的本底噪声和最佳性能,设计者必须了解元件级别的噪声源。保持良好的信噪比需要关注信号路径每一处细节的噪声。通过遵循以上步骤,便可成功调理小型模拟信号,并使用超高分辨率ADC将其转换。

相关文章推荐:

评论