数字频率计的设计

数字频率计是我们经常会用到的实验仪器之一,本实验要使用单片机和计数电路及液晶器件来设计一个宽频的数字频率计。

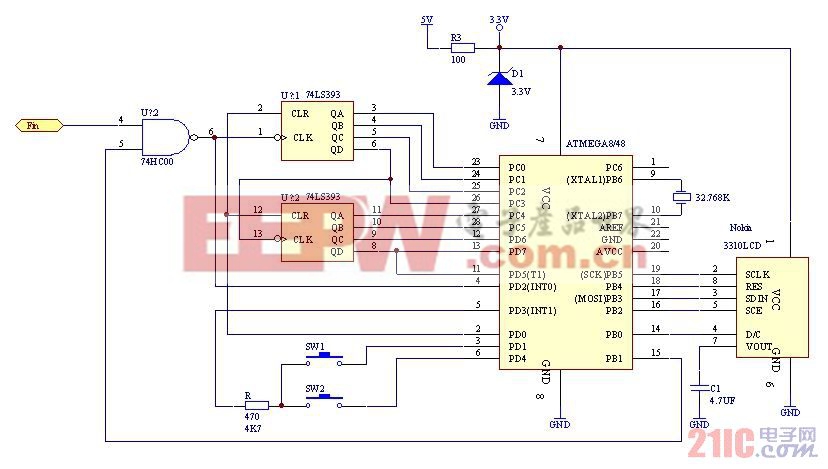

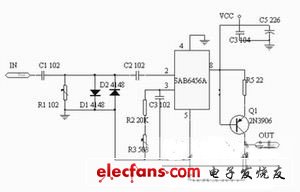

本文引用地址:http://www.amcfsurvey.com/article/185924.htm数字频率计的实验电路图(初步方案)

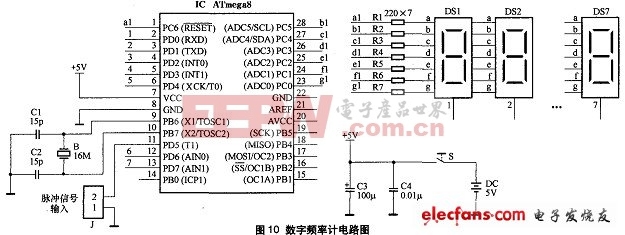

1) 数字频率计的计数及显示电路:

图1数字频率计的设计电路图

2)前置放大及分频电路

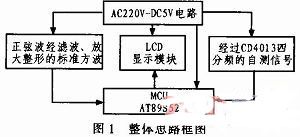

数字频率计的设计思路

频率的测量实际上就是在1S时间内对信号进行计数,计数值就是信号频率。用单片机设计频率计通常采用两种办法,1)使用单片机自带的计数器对输入脉冲进行计数,或者测量信号的周期;2)单片机外部使用计数器对脉冲信号进行计数,计数值再由单片机读取。

由于单片机自带计数器输入时钟的频率通常只能是系统时钟频率的几分之一甚至几十分之一,因此采用单片机的计数器直接测量信号频率就受到了很大的限制。

本实验电路采用方式2,使用一片74LS393四位双二进制计数器和Atmega8的 T1计数器组成了24位计数器,最大计数值为16777215。如果输入信号经过MB501分频器进行64分频后再进行测量,则固定1S时基下最高测量频率为1073.741760Mhz。

为了方便得到准确的1秒钟测量闸门信号,我们使用了Atmega8的异步实时时钟功能,采用32.768Khz的晶振由TC2产生1秒钟的定时信号。

数字频率计的测量原理

单片机打开测量闸门,即PB1输出高电平,同时TC2定时器启动。74LS393开始对输入脉冲进行计数,74LS393每计数达256时,Atmega8的T1计数器也向上计数1次。当1S定时到达时,单片机产生中断,PB1输出低电平关闭测量闸门,然后Atmega8读取74LS393和T1的计数值,然后送LCD显示。

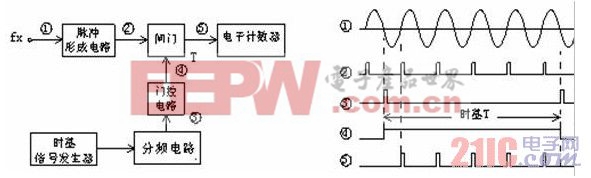

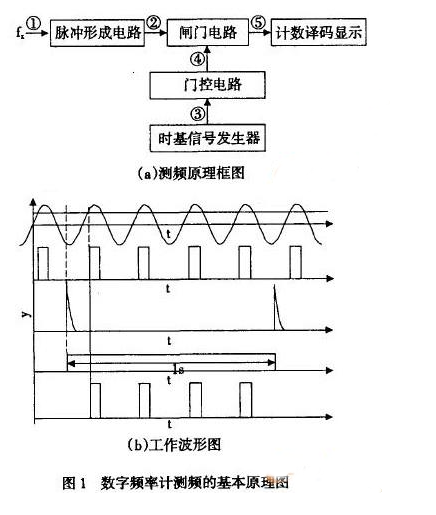

所谓“频率”,就是周期性信号在单位时间变化的次数。电子计数器是严格按照f=N/T的定义进行测频,其对应的测频原理方框图和工作时间波形如图1 所示。从图中可以看出测量过程:输入待测信号经过脉冲形成电路形成计数的窄脉冲,时基信号发生器产生计数闸门信号,待测信号通过闸门进入计数器计数,即可得到其频率。若闸门开启时间为T、待测信号频率为fx,在闸门时间T内计数器计数值为N,则待测频率为

fx = N/T (1)

若假设闸门时间为1s,计数器的值为1000,则待测信号频率应为1000Hz或1.000kHz,此时,测频分辨力为1Hz。

本实验的闸门时间分为为4档:1s,100ms,10ms,1ms。

图2 测频原理框图和时间波形

更多资讯请关注:21ic模拟频道

电路图符号相关文章:电路图符号大全

分频器相关文章:分频器原理 尘埃粒子计数器相关文章:尘埃粒子计数器原理 晶振相关文章:晶振原理

评论