使用赛灵思Vivado设计套件的九大理由

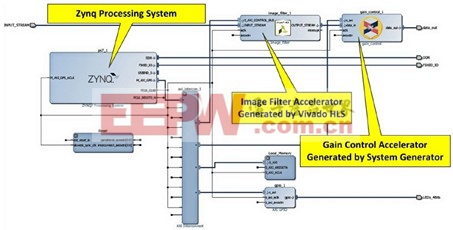

图8显示的是系统级设计在Vivado IP集成器中的视图,这个系统采用了一个赛灵思Zynq-7000处理系统、Vivado HLS生成的图像滤波器加速器和一个用Vivado System Generator for DSP生成的增益控制加速器。

本文引用地址:http://www.amcfsurvey.com/article/185311.htm

图8:用Vivado HLS和System Generator加速器完成的Zynq设计

Zynq-7000处理系统 Vivado HLS生成的图像滤波器加速器

System Generator生成的增益控制加速器

加速系统验证

理由七:用于设计和仿真的Vivado集成设计环境

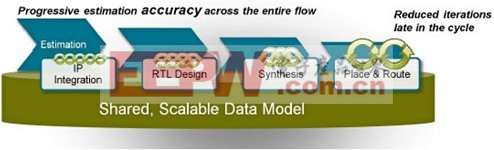

Vivado设计套件还提供完整的全集成成套工具,用于在先进的集成设计环境(IDE)中完成设计输入、时序分析、硬件调试和仿真工作。Vivado设计套件的集成设计环境的这种设计分析功能采用共享的可扩展数据模型,以容纳超大型All Programmable器件。Vivado设计套件在整个设计流程中使用这一单一的数据模型,让设计团队能够尽早在整个设计流程中随时掌握时序、功耗、资源利用率、路由拥塞等关键设计指标。估算也会随着设计流程的推进越来越准确,从而在减少设计迭代次数的同时推动更快完成设计收敛。

图9:VIVADO设计套件在整个设计流程中至始至终使用一个共享的可扩展数据模型

Vivado设计套件是唯一在自身的集成设计环境中提供混合语言仿真器的设计解决方案。而同类竞争仿真器的用户必须或选择VHDL仿真,或选择Verilog仿真。对集成众多厂商提供的IP的最新系统设计来说,混合语言仿真器至关重要。

Vivado设计套件的仿真和调试使用相同的波形观测仪,这样可以避免从仿真环境切换到硬件调试环境后还需要重新学习。竞争解决方案往往迫使用户学习和使用不同波形的工具来完成相同工作。在仿真功能和调试功能全集成的情况下,设计团队能够更快地完成工作,且避免出错,使用Vivado设计套件就是这种情况。

类似地,同类竞争开发工具的交叉探测功能呈碎片化且极度有限。此外这些交叉探测功能一般局限于某种单一的工具。与此对比鲜明的是,Vivado设计套件提供的全面、集成式front-to-back交叉探测功能,适用于所有不同设计视图,诸如实现设计、综合设计、时序报告,甚至还可追溯到设计团队的原始RTL代码。

由于Vivado设计套件使用单一数据模型架构,所以可在各种设计资源、原理图视图、层级浏览器、设计报告、消息、布局规划和Vivado器件编辑器(Vivado Device Editor)之间进行大范围交叉探测。借助这种独特的功能,可以即时反馈整个系统开发过程中发现的任何设计问题,从而加快调试,快速完成时序收敛。

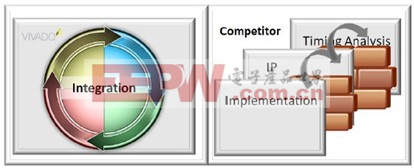

此外,竞争性设计解决方案使用多个磁盘文件用于工具间通信。使用多个磁盘文件带来的复杂性和低效率不仅会降低工具性能,而且还会造成多重接口,从而显著增大工具间沟通不畅的几率。然而,Vivado设计套件则不存在这种问题。它采用单一的共享数据模型处理设计的各方面工作,如图10所示。

图10:Vivado设计套件的单一共享数据模型平滑地集成各类设计工作

同类竞争设计解决方案 时序分析

集成 IP

实现

理由八:综合而全面的硬件调试

Vivado设计套件的探测方法直观、灵活、可重复。设计人员可选择最适合自己设计流程的探测策略:

♦ RTL设计文件、综合设计和XDC约束文件

♦ 网表插入

♦ 用于自动运行探测的互动式TCL或脚本

先进的触发器和采集功能

Vivado设计套件为检测复杂事件提供先进的触发器和采集功能。在调试进程中所有的触发器参数均可使用,用户可以实时检查或动态修改参数,且无需重新编译设计。

Zynq SoC支持处理器系统(PS)与可编程逻辑(PL)之间交叉触发

Vivado设计套件还支持Zynq-7000 All Programmable SoC器件内处理器系统(PS)与可编程逻辑(PL)之间的交叉触发。有了这项功能,结合使用赛灵思软件开发套件(SDK)、Vivado IP集成器和Vivado逻辑分析器(Vivado Logic Analyzer),可以协同调试同时使用Zynq处理器系统和可编程逻辑的嵌入式设计。再搭配强大的软件调试器GNU Debugger(GDB)实用工具,设计人员使用Vivado IP集成器和Vivado逻辑分析器可以同步调试软/硬件算法。Zynq-7000 All Programmable SoC平台和赛灵思ILA(集成逻辑分析器)IP核间提供有特定的接口信号,可支持无缝协同调试操作。

实现硬件实时读/写操作 — JTAG to AXI Master

Vivado设计套件可在硬件调试过程中实时地完成Zynq处理器系统和可编程逻辑间的读/写事务处理。最新调试IP核(JTAG to AXI Master)与简便易用的IP Integrator流相结合,能够在设计中访问任何基于AXI的IP模块中的数据。

c++相关文章:c++教程

评论