利用低门限电压延长电池寿命技术

多年以来,从事电源管理业务的半导体制造商尽力跟上终端系统用户的需求。越来越多的便携式电子产品在功能上花样翻新,这些产品需要峰值性能,要求设计者在设备的物理尺度内实现尽可能高的效率。虽然电池行业努力开发具有比传统镍镉(NiCd)电池电量更高的替代电池技术,但还远不能满足新一代便携设备对能量的需求。因此,便携式应用不得不寻求在低功耗电路设计上的创新开发,使设计工程师可以让终端系统以尽可能高的效率使用电池资源。在便携式设备中,元器件是功耗预算的主要部分,而且很显然,要跟上需求的变化,半导体器件制造商需要不断创新,帮助降低便携式产品的功耗。

本文引用地址:http://www.amcfsurvey.com/article/180861.htm以手机为例,降低模拟和数字基带芯片等手持设备中主要器件的工作电压是降低功耗的办法之一。在不需要DSP或微处理器发挥最大性能的时候,可以降低内核供电电压,并且降低时钟频率。越来越多的新一代低功耗应用采用了此项技术,以尽可能地节约系统能量。公式PC~(VC)2.F描述了一个DSP内核的功耗,这里,PC是内核的功耗,VC 是内核电压,F是内核时钟频率。降低内部时钟频率可以减少功耗,降低内核供电电压可以把功耗降得更多。

先进的硅片和封装技术能起到什么作用

有很多音箱新兴高耗电便携式设备性能的设计因素,本文将主要以在低电压应用中最常见的功率开关功率MOSFET为例,说明最新的硅技术突破在增加电源需求上的影响。为说明这些技术进步的影响,有必要了解功率MOSFET的一些关键参数。

通道的导通电阻(rDS(on))是由通道的横向和纵向电场控制的。通道电阻主要由栅源电压差决定的。当VGS超过门限电压(VGS(th)),FET开始导通。许多操作要求开关接地点。功率MOSFET通道的电阻与由公式R= L/A确定的物理尺寸有关,这里是电阻率,L是沟道长度,A是W x T,即沟道的横截面积。

在通常的FET结构中,L和W是由器件的几何尺寸确定的,而沟道厚度T是两个耗尽层之间的距离。耗尽层的位置会随栅源偏置电压或漏源电压而变。耗尽层的位置会随栅源偏置电压或漏源电压而变。当T在VGS和VDS的影响下减小到零时,两个对边的耗尽层就会连在一起,增加的沟道电阻(rDS(on))会接近无穷大。

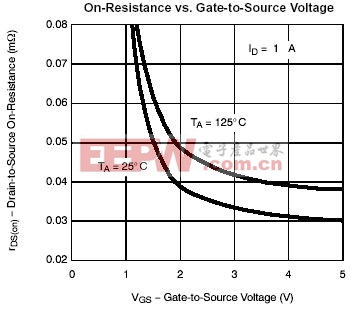

图1是rDS(on)与VGS特性的关系曲线。区域1对应的是累积电荷不足以产生反向的情况。区域2对应的条件是有足够的电荷,使P区的一部分反向并形成沟道,但这还不够,因为“空间电荷”效应也是很重要的。区域3对应的是电荷有限的情况,当栅体电势升高时,rDS(on)没有明显变化。

图 1: rDS(on) 与VGS 特性的关系曲线

评论