基于数据选择器和D触发器的多输入时序电路设计

1 基本原理

1.1 基本多输入时序网络

1.1.1 多输入时序网络的基本形式

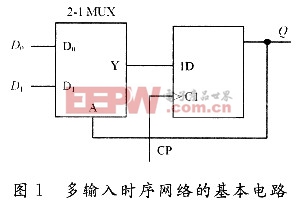

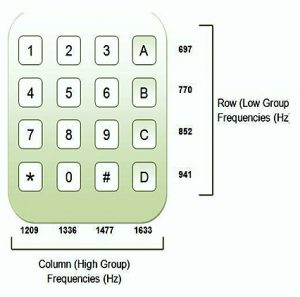

用1个D触发器和1个2选1数据选择器构成多输入时序网络的基本电路,如图1所示。

图1中,触发器的现态输出Qn作为数据选择器的A选择输入变量,数据选择器的Y输出作为触发器的D输入信号,数据选择器的输入端D0,D1作为所构成时序网络的外部信号输入端。

1.1.2 多输入时序网络基本电路的状态方程

由D触发器的特性方程Qn+1=D、数据选择器的输出逻辑表达式![]() 的关系,得多输入时序网络基本电路的状态方程:

的关系,得多输入时序网络基本电路的状态方程:

![]()

写成矩阵形式为:

1.1.3 已知状态转换关系确定时序网络输入矩阵参数的方法

由式(1)、式(2)有:

(1)现态Qn=0时,Qn+1=D0,选择输入D0,由状态转换关系确定D0。可实现所要求的状态转换:

若Qn+1=O,即状态转换为0→O,则式(2)中的输入矩阵应填D0=0;

若Qn+1=1,即状态转换为O→1,则式(2)中的输入矩阵应填D0=使状态产生变化的输入变量。

评论