高速ADC电源设计方案选择

本文介绍对于了解高速ADC电源设计至关重要的各种测试测量方法。为了确定转换器对供电轨噪声影响的敏感度,以及确定供电轨必须处于何种噪声水平才能使ADC实现预期性能,有两种测试十分有用:一般称为电源抑制比(PSRR)和电源调制比(PSMR)。

本文引用地址:http://www.amcfsurvey.com/article/178945.htm何谓电源抑制

当供电轨上有噪声时,决定ADC性能的因素主要有两个,它们是PSRR-dc、PSRR-ac和PSMR。PSRR-dc指电源电压的变化与由此产生的ADC增益或失调误差的变化之比值,它可以用最低有效位(LSB)的分数、百分比或对数dB (PSR = 20 × log10 (PSRR))来表示,通常规定采用直流条件。

但是,这种方法只能揭示ADC的一个额定参数随电源电压可能会如何变化,因此无法证明转换器的稳定性。更好的方法是在直流电源之上施加一个交流信号,然后测试电源抑制性能(PSRR-ac),从而主动通过转换器电路耦合信号(噪声源)。这种方法本质上是对转换器进行衰减,将其自身表现为杂散(噪声),它会以某一给定幅度提升至超过转换器的噪声基底值。其意义是表明在注入噪声和幅度给定的条件下转换器何时会崩溃。同时,这也能让设计人员了解到多大的电源噪声会影响信号或加入到信号中。PSMR则以不同的方式影响转换器,它表明当与施加的模拟输入信号进行调制时,转换器对电源噪声影响的敏感度。这种影响表现为施加于转换器的IF频率附近的调制,如果电源设计不严谨,它可能会严重破坏载波边带。

总之,电源噪声应当像转换器的任何其它输入一样进行测试和处理。用户必须了解系统电源噪声,否则电源噪声会提高转换器噪声基底,限制整个系统的动态范围。

电源测试

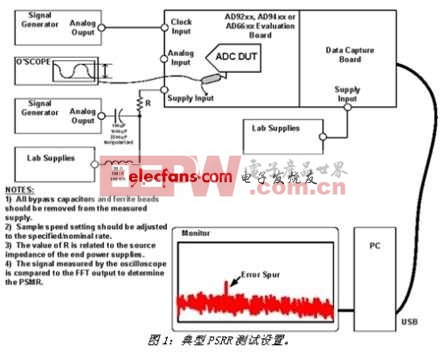

图1所示为在系统板上测量ADC PSRR的设置。分别测量每个电源,以便更好地了解当一个交流信号施加于待测电源之上时,ADC的动态特性。开始时使用一个高容值电容,例如100uF非极化电解质电容。采用1mH的电感来充当直流电源的交流阻断器,一般将它称为“偏置-T”,可以购买采用连接器式封装的产品。

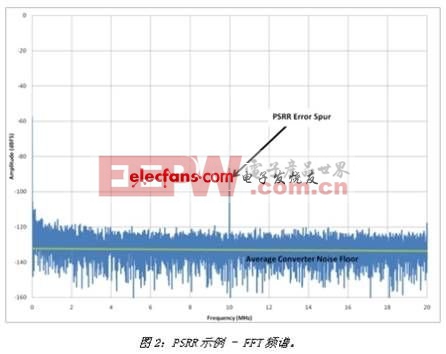

使用示波器测量交流信号的幅度,将一个示波器探针放在电源进入待测ADC的电源引脚上。为简化起见,将施加于电源上的交流信号量定义为一个与转换器输入满量程相关的值。例如,如果ADC的满量程为2Vpp,则使用200mVpp或-20dB。接下来让转换器的输入端接地(不施加模拟信号),查找噪声基底/FFT频谱中处于测试频率的误差杂散,如图2所示。若要计算PSRR,只需从FFT频谱上所示的误差杂散值中减去–20dB即可。例如,如果误差杂散出现在噪声基底的-80dB处,则PSRR为-80dB - (-20dB),即-60dB(PSRR = 误差杂散(dB)- 示波器测量结果(dB))。-60dB的值似乎不太正常,但如果换算成电压,它相当于1 mV/V(或10-60/20),这个数字对于任何转换器数据手册中的PSRR规格而言都并不鲜见。

下一步是改变交流信号的频率和幅度,以便确定ADC在系统板中的PSRR特性。数据手册中的大部分数值是典型值,可能只针对最差工作条件或最差性能的电源。例如,相对于其它电源,+5 V模拟电源可能是最差的。应确保所有电源的特性都有说明,如果说明得不全面,请咨询厂家。这样,设计人员将能为每个电源设置适当的设计约束条件。

请记住,使用LC配置测试PSRR/PSMR时有一个缺点。当扫描目标频段时,为使ADC电源引脚达到所需的输入电平,波形发生器输出端所需的信号电平可能非常高。这是因为LC配置会在某一频率(该频率取决于所选的值)形成陷波滤波器。这会大大增加陷波滤波器处的接地电流,该电流可能会进入模拟输入端。要解决这一问题,只需在测试频率造成测量困难时换入新的LC值。这里还应注意,LC网络在直流条件下也会发生损耗。记住要在ADC的电源引脚上测量直流电源,以便补偿该损耗。例如,+5V电源经过LC网络后,系统板上可能只有+4.8V。要补偿该损耗,只需升高电源电压即可。

评论