基于SOI高压集成技术的电平位移电路设计

随着智能功率IC的发展.其应用领域和功能都在不断地扩展。而作为智能功率IC中的重要一类栅驱动IC在功率开关、显示驱动等领域得到广泛应用。在栅驱动电路中需要电平位移电路来实现从低压控制输入到高压驱动输出的电平转换。而在一些领域如SOC中的待机模式激活、ESD保护等需要能工作在负电源的电平位移电路。

本文引用地址:http://www.amcfsurvey.com/article/178691.htmSOI(Silicon-On-Insulator)技术以其高速、低功耗、高集成度、极小的寄生效应以及良好的隔离等特点,在集成电路设计应用中倍受青睐。其优良的介质隔离性能使得智能功率IC中高低压器件的隔离更为完善。

本文基于SOI高压集成技术设计了电源电压为8~-100V的电平位移电路,并对电路中的核心LDMOS器件进行了设计和模拟仿真优化。

1 电路结构

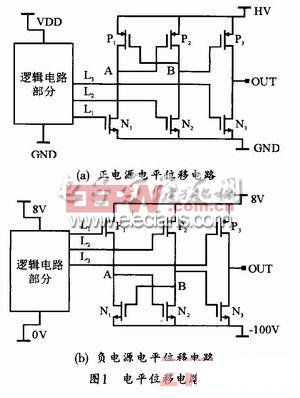

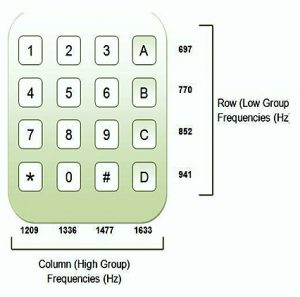

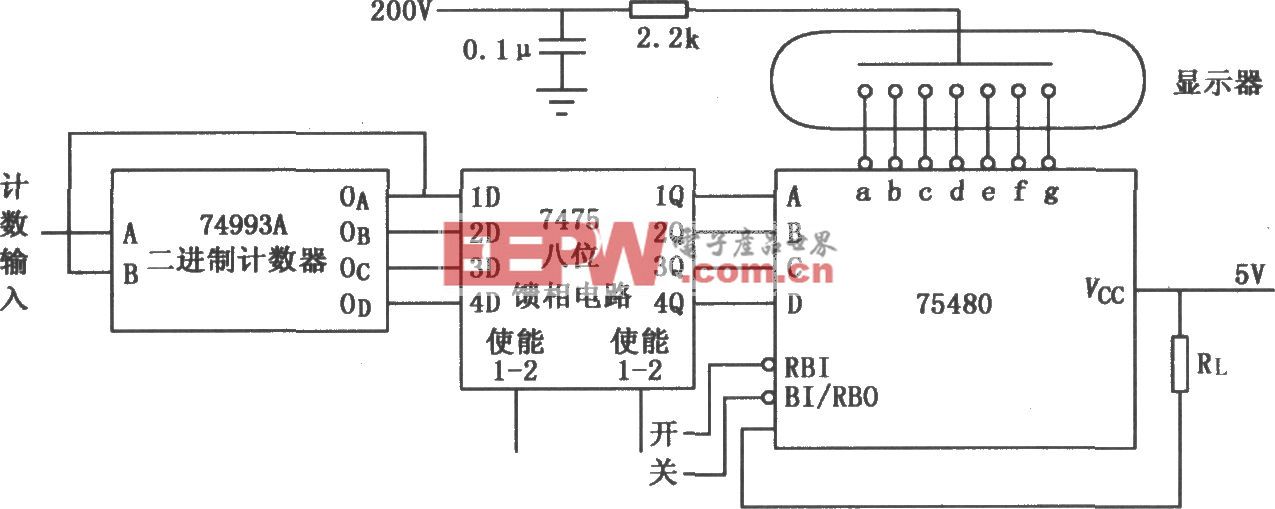

传统正电源应用的电平位移电路结构如图1(a)所示。L1、L2、L3是由逻辑电路部分产生的低压时序控制信号,N1、N2、N3为高压nLDMOS器件,P1、P2、P3为高压平pLDMOS器件。由P1,P2和N1、N2构成的电平位移单元将L1、L2的低压逻辑信号转变为可以控制P3管的高压电平,与L3一起控制由P3和N3组成的反向输出级,从而实现从低压逻辑信号到高压驱动输出的转换。

在正电源电平位移电路中,由于nLDMOS的源极为低压,所以可以通过低压逻辑部分来控制其开关状态,而源极为高压的pLDMOS则通过电平位移来控制。当高压驱动电压为8~-00V,低压逻辑部分工作电压为0~8V时,电平位移转换部分的电压分布本身没有改变,但是在和低压控制端接合时,与传统的正电源相比电平发生了改变,就需要重新设计低压逻辑的控制方式。此时,nLDMOS的源极为-100V电压,显然不能通过低压逻辑控制部分的0~8V电压来实现控制,而pLDMOS的源极为8V电源。因此采用了低压逻辑输出直接控制pLDMOS,而nLDMOS则通过电平位移来控制的方法,如图1(b)所示。

评论