PCB 板 EMC/EMI 的设计技巧

2.6 电源平面的分割处理

* 电源层的分割

在一个主电源平面上有一个或多个子电源时,要保证各电源区域的连贯性及足够的铜箔宽度。分割线不必太宽,一般为20~50mil线宽即可,以减少缝隙辐射。

* 地线层的分割

地平面层应保持完整性,避免分割。若必须分割,要区分数字地、模拟地和噪声地,并在出口处通过一个公共接地点与外部地相连。

为了减小电源的边缘辐射,电源/地平面应遵循20H设计原则,即地平面尺寸比电源平面尺寸大20H(见图2),这样边缘场辐射强度可下降70% 。本文引用地址:http://www.amcfsurvey.com/article/178433.htm

3 EMI的其它控制手段

3.1 电源系统设计

* 设计低阻抗电源系统,确保在低于fknee频率范围内的电源分配系统的阻抗低于目标阻抗。

* 使用滤波器,控制传导干扰。

* 电源去耦。在EMI设计中,提供合理的去耦电容,能使芯片可靠工作,并降低电源中的高频噪声,减少EMI。由于导线电感及其它寄生参数的影响,电源及其供电导线响应速度慢,从而会使高速电路中驱动器所需要的瞬时电流不足。合理地设计旁路或去耦电容以及电源层的分布电容,能在电源响应之前,利用电容的储能作用迅速为器件提供电流。正确的电容去耦可以提供一个低阻抗电源路径,这是降低共模 EMI的关键。

3.2 接地

接地设计是减少整板EMI的关键。

* 确定采用单点接地、多点接地或者混合接地方式。

* 数字地、模拟地、噪声地要分开,并确定一个合适的公共接地点。

* 双面板设计若无地线层,则合理设计地线网格很重要,应保证地线宽度》电源线宽度》信号线宽度。也可采用大面积铺地的方式,但要注意在同一层上的大面积地的连贯性要好。

* 对于多层板设计,应确保有地平面层,减小共地阻抗。

3.3 串接阻尼电阻

在电路时序要求允许的前提下,抑制干扰源的基本技术是在关键信号输出端串入小阻值的电阻,通常采用22~33Ω的电阻。这些输出端串联小电阻能减慢上升/下降时间并能使过冲及下冲信号变得较平滑,从而减小输出波形的高频谐波幅度,达到有效地抑制EMI的目的。

3.4 屏蔽

* 关键器件可以使用EMI屏蔽材料或屏蔽网。

* 对关键信号的屏蔽,可以设计成带状线或在关键信号的两侧以地线相隔离。

3.5 扩频

扩展频谱(扩频)的方法是一种新的降低EMI的有效方法。扩展频谱是将信号进行调制,把信号能量扩展到一个比较宽的频率范围上。实际上,该方法是对时钟信号的一种受控的调制,这种方法不会明显增加时钟信号的抖动。实际应用证明扩展频谱技术是有效的,可以将辐射降低7到20dB。

3.6 EMI分析与测试

* 仿真分析

完成PCB布线后,可以利用EM I仿真软件及专家系统进行仿真分析,模拟EMC/EMI环境,以评估产品是否满足相关电磁兼容标准要求。

* 扫描测试

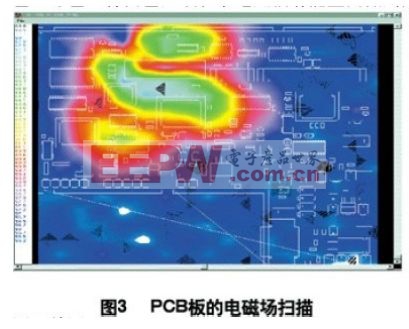

利用电磁辐射扫描仪,对装联并上电后的机盘扫描,得到PCB中电磁场分布图(如图3,图中红色、绿色、青白色区域表示电磁辐射能量由低到高),根据测试结果改进PCB设计。

4 小结

随着新的高速芯片的不断开发与应用,信号频率也越来越高,而承载它们的PCB板可能会越来越小。PCB设计将面临更加严峻的EMI挑战,唯有不断探索、不断创新,才能使PCB板的EMC /EMI设计取得成功。

评论