一种单级长延时电路的设计

摘要:设计了一款单级长延时产生电路。此长延时产生电路,对输入的低脉宽宽度没有要求,一次展宽到位,同时通过精准的电流源设计,采用工艺偏差比较小的电容,消耗极小的版图面积,提高了信号精度,电路在TSMC0.35微米工艺得到验证,达到设计效果。

关键词:延时;脉宽;异步时序;只读存储器

调查显示,在整个世界范围内,存储器芯片的交易大概占了半导体交易的三分之一,存储器成为数字产品中重要组成部分。存储器的存储速度、功耗成为存储器芯片研发中重要指标。存储器电路根据不同的应用和不同的存储方式分成了各种不同的种类,包括SRAM,DRAM,ROM.EPROM,FLASH和FRAM等。随着电子设备的发展,电子设备的存储容量越做越大,存储密度也越来越高。存储密度的不断发展,快速推动了半导体工艺的发展,使半导体工艺的特征尺寸越做越小。同时存储器基本单元结构也不断创新和缩小,从典型的8T、6T到一个单管。

随着特征尺寸的减小,芯片存储密度的增大,仔储器读写速度的不断提高,存储器渎写时位线上的寄生电容越来越成为芯片读取速度的关键。大的位线电容导致读取数据时,电容的充放电变得缓慢,严重制约着存储器读写速度。现在大规模的存储器的数据读写,一般都需要上下预充电和灵敏放大器的参与。灵敏放大器的类型分为:电压灵敏放大器和电流灵敏放大器。上下预充电和灵敏放大器的应用使存储器的读写一般都采用异步时序进行读写。先通过地址检测器,产生地址检测信号,再使用地址检测信号产生一些列错开的时序控制信号。控制信号分别对预充电电路、基本存储单元、灵敏放大器、输入输出锁存器进行异步时序控制。控制信号需要进行延迟处理、展宽处理和错位处理。因存储器的容量的急剧增大,每一位线上带的基本存储单元也相应增加,存储位线上的电容变得显著。导致灵敏放大器读写时间增加。因此预充电的工作和灵敏放大器的工作需要更宽的电平脉冲,同时灵敏放大器的脉冲要在预充电脉冲之后。用RC延时产生展宽脉宽,每一级最多展宽到输入信号脉宽的两倍。需要多级展宽才能得到适合的宽脉宽。并且用RC产生长延时信号需要几级RC电路且每一级RC之间还需要有缓冲器,同时输入脉冲不能太窄,否则状态容易在不同的工艺角上出现飘掉的可能。同时多级的RC消耗比较大的芯片面积。本文在分析传统多级RC输入低脉冲展宽电路原理基础上,用单级的思想设计了单级长延时电路。

1 传统多级RC输入低脉冲展宽电路

1.1 传统低脉冲展宽电路原理分析

传统低脉冲展宽电路如图1所示,输入Vin为低的窄脉冲,令其脉冲宽度为Win,第一级的输出V1,令其脉冲宽度为W1,第二级的输出V2,令其脉冲宽度为W2,第i-1级的输出为Vi-1,令其脉冲宽度为VOUT,最后输出脉冲,另其脉冲宽度为WOUT。

则经过第一级的脉宽展宽为:W1=Win+R1C1且R1C1Win。

经过第二级的脉宽展宽为:W2=W1+R2C2且R2C2W1。

经过第i级的脉宽展宽为:Wi-1=Wi-2+Ri-1Ci-1且Ri-1Ci-1Wi-2。

最后输出脉宽展宽为:WOUT=Wi-1+RiCi且RiCiWi-1。

由上面分析可知,多级RC输入低脉冲展宽电路,首先对输入脉冲宽度有要求,如果输入脉宽太窄,比如说1ns的延时,则要得到12ns的脉宽至少要4级,且每一级的RC延迟要小于这级的输入低脉冲宽度,否则产生的输出脉宽在中间将断开,分成两个相隔的输入低脉冲,同时如果Vin低脉冲太窄,则不能使电容的电压充到使反相器状态发生翻转的最低高电平处,则与门的一端输入一直为高,另一端为Vin,因此不能使输入的窄脉冲发生展宽。

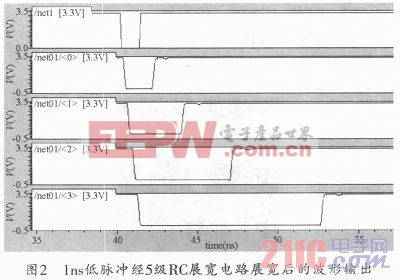

此RC多级脉宽展宽电路,需要耗费比较大的芯片版图面积。下面假设输入为1ns的低脉冲,5级RC延时展宽电路,仿真得到的结果如图2。

可知窄的低脉冲需要多级才能展开到一定的脉冲宽度,而且每一级必须保证RC延迟小于输入脉冲本身的宽度,否则输出脉冲不能连续。

DIY机械键盘相关社区:机械键盘DIY

电流传感器相关文章:电流传感器原理 脉冲点火器相关文章:脉冲点火器原理

评论