用于计算应用的占位面积优化功率器件

I.概述

本文引用地址:http://www.amcfsurvey.com/article/177087.htm本文将:

. 总结针对计算应用的典型同步降压调节器负载设计规范;Tjcn、负载电流、DC和瞬态调节

. 简单概述带来典型的每相20 - 30 A电流的因素;工作频率、瞬态响应和效率

. 解释三要素概念=>额定输出电流由三个因素确定:输出功率/电流、效率,以及Tjcn-amb热阻抗

. 总结功率级(Power Stage)器件设计特性,优化效率和热阻抗

. 展示在效率、功率损耗和温升等方面的测量数据

. 解释采用如何测量安装在电源板上的零部件的热阻抗

. 探讨受输出电压影响的效率和热阻抗,及所产生的HS/LS占空比(duty cycle)

. 结论

II.典型的同步降压计算负载规范

针对典型的同步降压调节器计算负载需求,对功率级系列部件进行优化。这些应用将具有大范围的电流水平且可以是单相或者多相。通过在每相基准上比较电源系统(power train)规范,我们注意到,许多设计显示了共同的工作范围。典型的每相电源系统规范为:

. 电源系统占空比为5 % - 40 %

. 工作频率:300 kHz到600 kHz

. 负载功率:25 W

. 负载电流:25 A

针对此设计范围,已对部件的功率级设定进行了优化。选择了最通用的设计作为目标工作点- 12 Vin, 1 V / 25 A 输出。

III.决定负载规范的因素

上述的参考设计规范—占空比、频率、功率和电流—是通过平衡相当广泛的电气和散热限制来设定的。对于典型的多相CPU电源,这些限制包括:

. 静态负载运行期间的输出峰峰值电压纹波

. 负载瞬变期间的输出电压偏移

. 系统温升极限

. 硅Tjcn设计极限

. 输入电流纹波

将会讨论每个设计因素的影响,以及折衷方案如何推动电源系统规范达到每相电流极限和工作频率。

满足这些系统性能目标需要平衡相互冲突的要求。对于稳态和瞬态负载,设计必须具有低输出电压纹波。每相DC电流、峰峰值纹波电流和工作频率都会影响输出调节。通过增加电源系统电感,可以减少静态输入和输出纹波,但较大的电感将会降低供电瞬态性能。较高的工作频率将减少纹波并改进瞬态性能,但较高的工作频率将会引起效率降低,因为增加了开关损耗,由此增加了器件的温升。

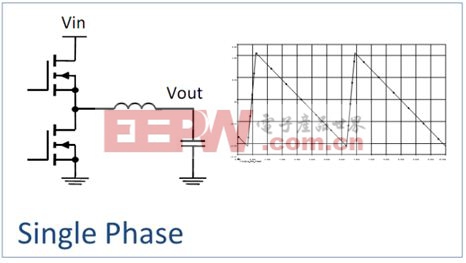

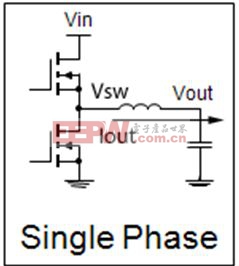

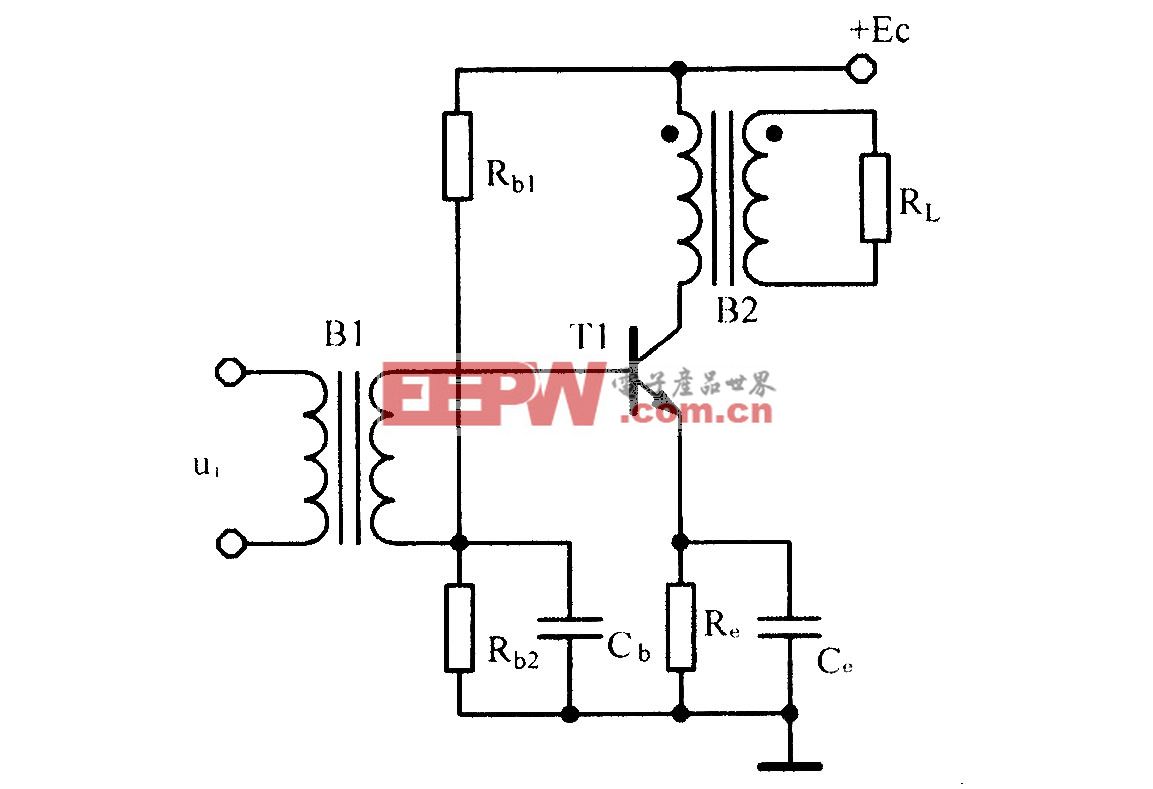

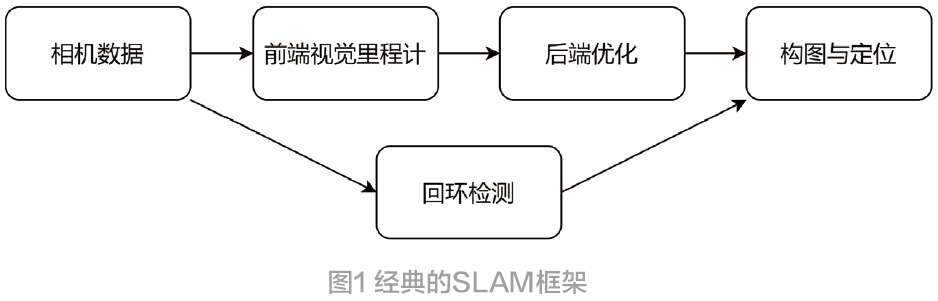

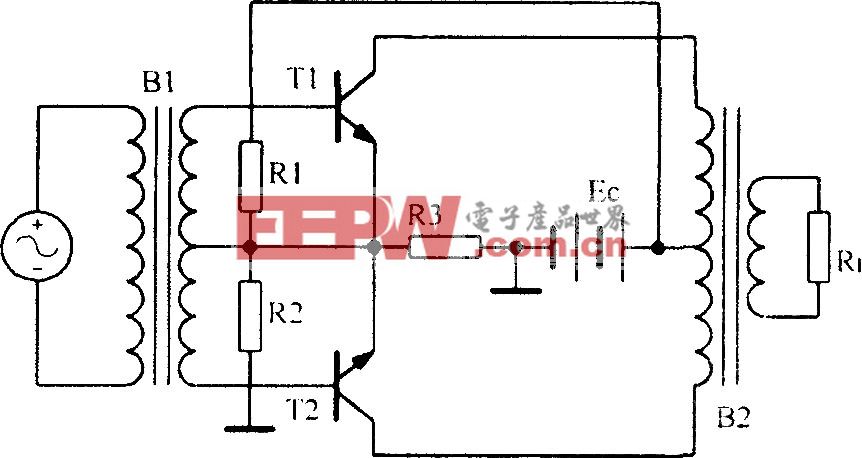

用于解决此局限的设计方法就是将总负载电流分成几个并联的电源系统,且允许每个都有相对高的纹波电流值。图1和图2显示了单相设计与多相设计的纹波电流比较。

图1. 单相纹波电流

图2. 多相纹波电流

多相设计的优势为几个低频单相电源系统的电流交错。这带来了较低的峰峰值纹波和较高的纹波频率。对于给定的纹波电压,还允许减少输出电容数。对于每一个电源系统,可以使用小电感来实现良好的瞬态响应。但这将导致纹波的增加。通过相电流的交错,将减少产生的输出电流纹波,同时仍然允许良好的瞬态响应。另外,大多数控制器具有瞬态运行模式,允许对准各个相位,用于优化转换速率。

对于给定的电感/电容元件的设置,较高的工作频率将导致纹波减少并改进瞬态响应;或者设计人员可以选择保持纹波恒定,并减少电感和输出电容元件的尺寸。

注意,通过增加电源频率或减少输出电感,无法单独满足CPU负载的初始急速瞬态阶段要求。需要低阻抗陶瓷电容的网格运作来满足初始瞬态。但在减少剩余的输出电容方面,更快的电源瞬态响应是有效的。

典型的每相25A、300kHz – 600kHz电源系统规格,是基于这些限制条件的最佳平衡。因此针对这一电流和频率范围所设计的器件将涵盖范围广泛的应用。

IV.三要素

当新的部件发布时,我们常常会询问它的额定电流。飞兆半导体的数据表使用行业标准方法来规定额定电流,基于元件放置在极大的散热器上,并测量每个芯片发热达到其额定Tjcn额定值时所需要的电流。这使得可替换元件之间容易比较,但在实际电源应用中对部件的有效电流能力的理解有些局限。

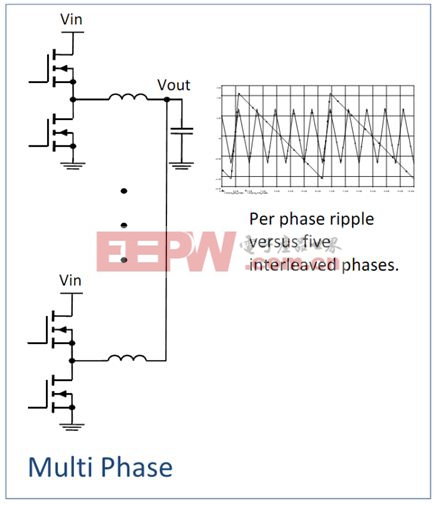

就像一只三条腿的凳子,部件的有效额定电流将基于三个不同因素的平衡:

. 输出功率

. 效率

. Jcn-Ambient 热阻抗

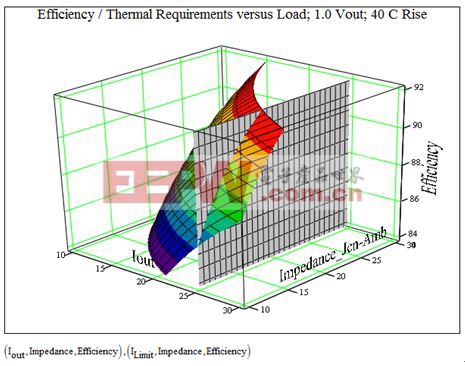

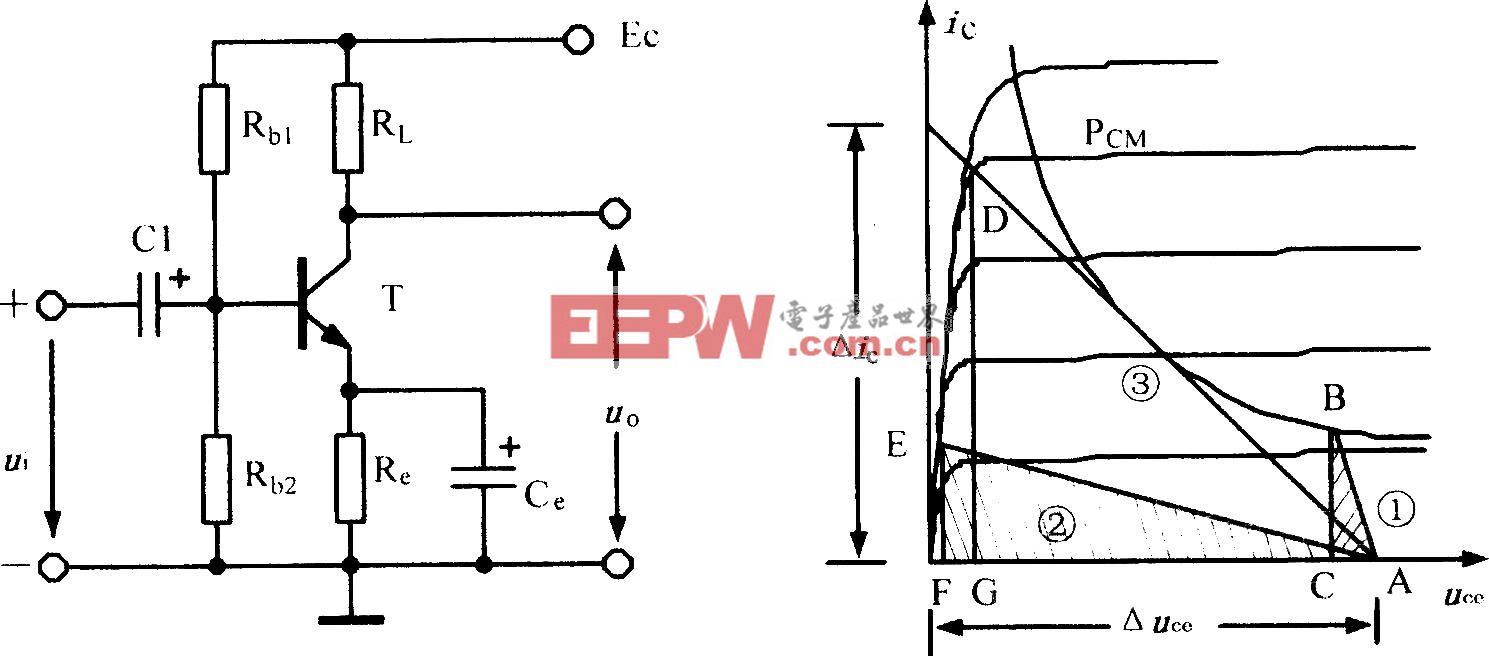

如图3所示,对于在期望的额定电流上运行的部件,它必须满足这三个限制因素的平衡;功率(Vout x Iout)、效率和热阻抗。图3中,25 A的灰色平面与曲面相交部分显示了在Vout = 1 V时,实现25 A所需的效率和阻抗组合。例如,假如设计的效率为90%,那么它必须具有低于14 C / W的热阻抗,以便保持温升低于40 C。

图3. 额定电流与效率和热阻抗的比较

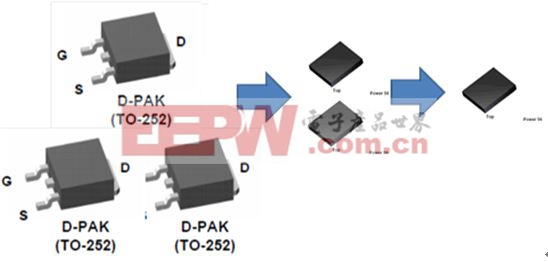

由于在过去的五年里器件性能得到了改进, 25 A输出设计已经从一个三或四个FET D-PAK设计演变为一个双FET结构,并且现在已经演变为单一的5 mm x 6 mm功率级双芯片。图4显示了在电源系统尺寸方面的显著减少,这些已在这段时间内发生。

图4. 对于25 A设计的电源系统演变

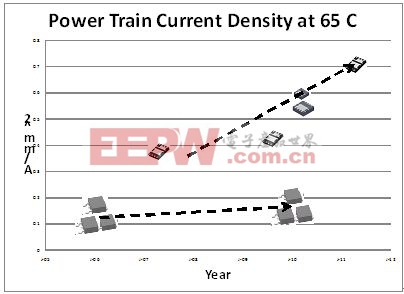

可以使用A/mm^2来表述此尺寸方面的改进,这里mm^2尺寸是安装部件所需的线路板面积尺寸。这包括封装外形加上焊接位占位面积。图5显示了在密度方面的演变,它们是从一系列飞兆评测板上观测到的,而这些评测板在过去五年里一直进行测试。

图5. 电源系统电流密度

在以下章节中,将回顾飞兆半导体能够实现功率密度的显著提高的设计改进。

V.功率级器件设计具有优化效率和热阻抗的特性

如图3所示,如果需要增加功率密度,就必须通过降低功率损耗、改进热阻抗或者同时改进这两者来提高FET效率。

回到图5中所引用的电源设置,可以标出它们的损耗。图6显示出对于图5中所引用的电源设置,损耗减少了。

图6.电源损耗

飞兆半导体最新发布的功率级部件显示了全系列产品的最佳功率密度性能。

功率级系列产品的功率改进是以FET效率和封装热阻抗设计这两者为基础的。

电源效率受以下因素影响:

. FET硅性能[1]

. 封装和线路板寄生参数[2][3]

影响硅器件最大负载性能的关键来源是低侧(Low Side,LS) FET传导损耗和高侧(High Side,HS) FET传导加开关损耗。LS FET的开关损耗也是一个重要因素。

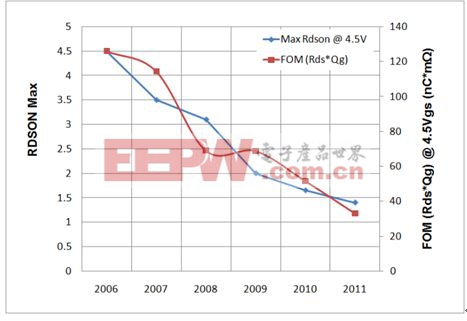

如图7所示为与时间相对应的Rds和Rds*Qg的改进,随着时间的推进,飞兆半导体已经在这两者上实现了显著改进。传导损耗与RDSON成正比,而开关损耗与Rds*Qg直接相关。因此,飞兆半导体实现的设计改进减小了这两个损耗因素。通过减少硅器件特有的导通电阻(m? cm2)来降低Rds。这提供了更多选项,可使用较小的芯片来达到期望的Rds。由于较小的芯片具有较低的栅极电荷,这还将带来较低的开关损耗。在开关损耗中起作用的其它指标还有Qgd、Coss、Rg和跨导(transconductance)。采用此新一代部件,飞兆半导体能够缩小芯片尺寸,并在全部指标设置上进行改进。

图7. 与时间对应的Rds和Rds*Qg改进

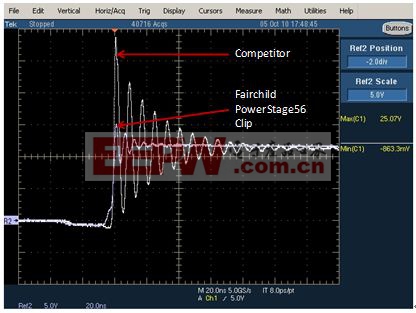

FET振铃性能是一个经常被忽视的因素,但也会影响效率。飞兆半导体的LV FET已包含了专有的(专利申请中)自衰减特性,可使峰值过冲和振铃持续时间最小化,如图8所示。采用典型的基于飞兆半导体器件的设计,则无需缓冲电路。对于竞争对手解决方案,其缓冲器可能降低最高效率多达1%。

图8.飞兆半导体FET中的内在缓冲器

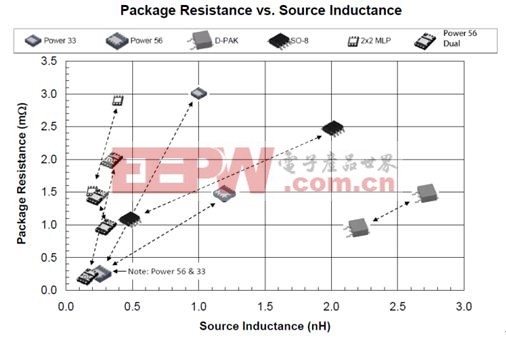

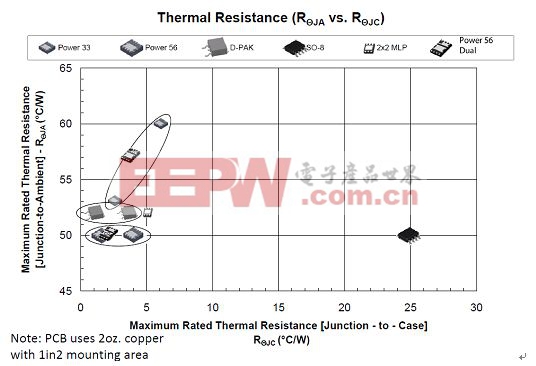

在电源性能中封装属性也起到关键作用。如图9和图10所示,显著的性能改进已经实现,因为封装设计已经从D-PAK / SO-8设计发展到分立Power56,然后到双Power56。D-PAK部件具有低热阻,但源极电感高。由于使用多源极粘接线,SO-8部件提供了低的源极电感,但Jcn-Case热阻抗高。

图9. 封装电阻对比源极电感

图10. 热阻Jcn-Ambient对比Jcn- Case

Power56系列则结合了这两者的最佳属性,具有良好的Jcn-Case热阻抗和低源极电感。如图11所示,Power56封装具有大导热面积与大量源极粘接线相结合的优势。

图11. D-PAK对比Power56结构

功率级双封装则将其带到了一个新的水平上,消除了HS和LS FET间的线路板寄生电阻和电感。单单此电感可以轻易达到0.1 – 0.2 nH,与分立Power 56封装的值基本相同。

图12显示了功率级非对称双FET设计的演变。该功率级在最小的占位面积封装中结合了分立FET D-PAK和SO-8设计的最佳特性。在该功率级中,HS FET结合了低电感的多源极粘接线和低热阻抗的金属漏极衬片。LS FET采用低热阻抗的大金属漏极衬片。飞兆半导体的第一代功率级部件使用多个粘接线来连接LS芯片源极。第二代使用固体金属夹来连接LS源极,从而改进封装热性能并减少LS源电感。功率级双FET设计也消除了HS和LS FET间的线路板互连电阻和电感。

图12. 功率级封装的演变

VI.针对效率、功率损耗和温升的测量数据

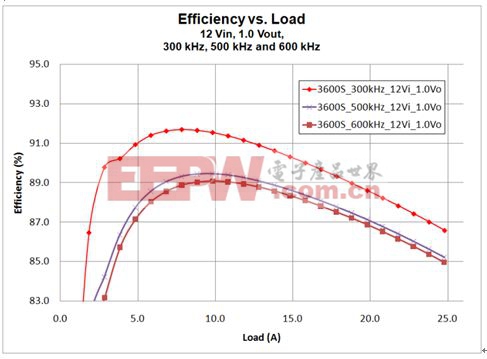

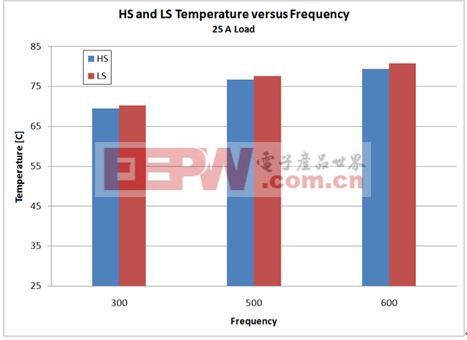

在FET FOM和封装结构中采用最新的重要改进,飞兆半导体现在能够在单一Power 56封装空间中提供25 A解决方案。图13和图14显示了在评估设计中测量的功率级部件的高效率和低工作温度。

图13. 功率级FDMS3600S的效率

图14. HS和LS器件的温度与频率对比

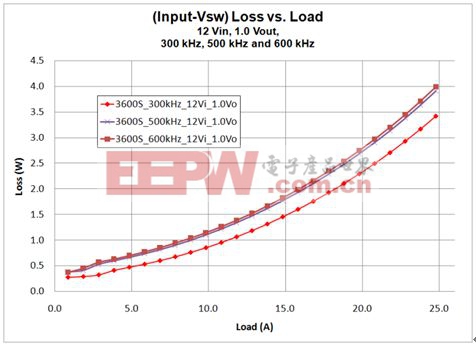

功率损耗通常从测试板的输入到输出中测得,但对于估算热负载,专注于FET损耗和Tjcn上所产生的温升是非常有用的。为做到这点,通过减去电感功率损耗来调整功率损耗估算值,如图15所示。对于飞兆半导体的效率测量,除了测量Vout,也可测量Vsw 的DC平均值。从功率损耗估算值中减去(Vsw-Vout)*Iout,可提供更好的FET损耗估算值。此近似值非常适用于中到大电流水平,这里电感RMS和DC电流接近相等。

图15. 估算电感损耗

图16显示了从测试板输入脚到输出电感的功率损耗。

图16. 输入-Vsw功率损耗

此损耗包括几个因素;栅极驱动器损耗、线路板传导损耗和FET损耗。在较高的功率水平上,温升成为限制,FET开关和传导损耗将占主要地位,还包括线路板铜损耗。在大负载下,栅极驱动损耗将不再是一个重要因素。

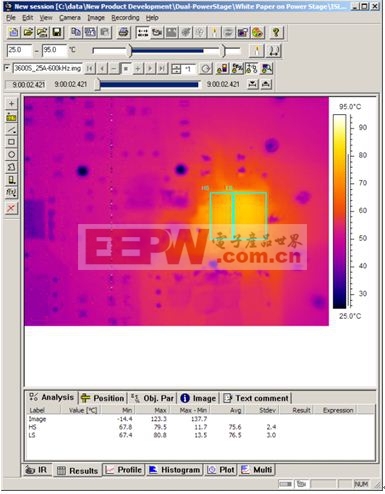

如图17所示,由于功率耗散和热阻抗不同,封装内的HS和LS将在略有不同的结温下工作。

图17. 在600 kHz, 25 A负载下的FDMS3600S

VII.热阻抗测量数据

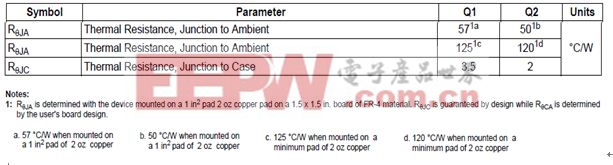

对于安装在标准测试板上的部件,功率级数据表将显示Jcn-Case和Jcn-Amb热阻抗规范。

图18. 热阻抗规范

但这些数值仅适用于安装在测试夹具上的双FET封装,且只有一个芯片供电。对于部件安装在电源板上的多FET,其性能和两芯片供电有着更复杂的关系。

如图18所指出的,Jcn-Amb阻抗将受Case-Amb成分的强大影响。这是电源板的热阻抗,且由实际的电源板设计来确定。一个额外的复杂因素就是设计内的功率耗散位置间的热耦合。如果HS和LS FET均有功率损耗,一个芯片的温升将感应第二个芯片的温升且成比例。估算所产生的芯片温度变化是一项困难的工作。

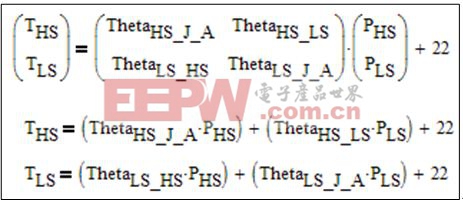

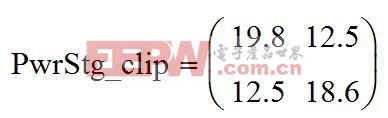

针对安装在实际应用板上的FET封装,飞兆半导体用于模拟交叉发热的方法就是测量热阻抗矩阵。

模拟两个FET的一个简单矩阵可以提供对热性能的很好的了解。一旦确定矩阵,对于任何HS和LS功率损耗组合,都可以计算单个FET芯片的温度。

图19显示了矩阵的一个实例,针对给出的HS/LS功率损耗比例,如何使用矩阵来计算单个芯片的温度。在此实例中,Tjcn假定为22 C。

图19. 热阻抗矩阵

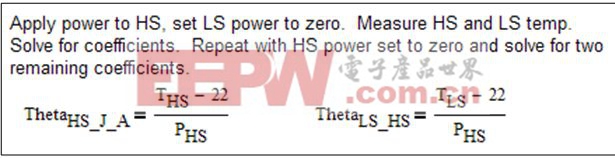

为求出矩阵中的单个元素,图19的公式改写为如图20中所示的公式。在此实例中,假定环境温度为22 C。

图20. 求出矩阵系数

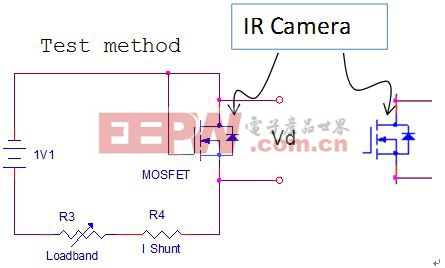

图20显示可以通过每次给一个器件供电来确定热矩阵的元素,然后测量板上安装部件的两个芯片所产生的温升。进行该测试的一个简便方法是,在一个FET的体二极管中施加电流,然后使用IR照相,测量两个FET的温度。图21所示为测试设置。

图21. 热阻抗测试方法

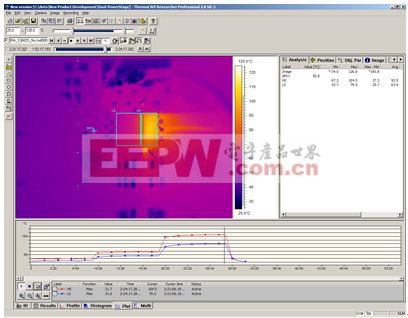

图22显示了一个测量实例。飞兆半导体通过使用自动化效率测量设备进行此测量,按照每步10分钟,逐步改变负载,通过几个功率水平。划出直线使其与所产生的数据相符,温度与功率测量值相比的斜率就是期望的矩阵值。

图22. 在功率级封装中使一个FET发热

此测量将描述安装在实际板上的部件热阻抗。为达到最好的准确度,不可去除关键功率元件,比如此测试中的输出电感。该电感将充当热流路径,并且将略微降低Jcn-Amb阻抗。

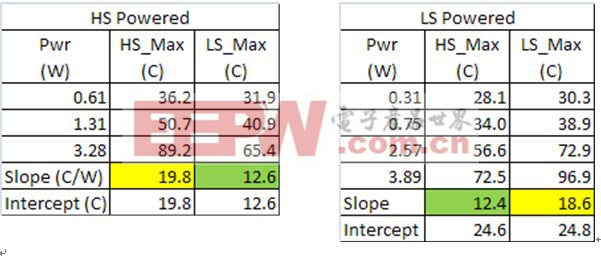

图23显示了此计算的一个实例。所产生矩阵的对角元素将会是每个芯片的Jcn-Amb阻抗,非对角元素将模拟芯片间的发热。图23和图24显示了测量数据和所产生的矩阵项实例。通过取两测量项平均值来计算非对角项。

图23. 计算热矩阵系数

图24. 测量热矩阵

因为HS芯片较小且封装片也较小,因而它的阻抗略高。

VIII.使用热矩阵作为分析工具

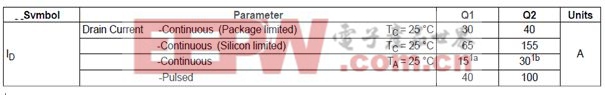

典型的FET数据表将列出几个不同数字作为器件的额定电流。图25显示了一组典型的规范值。这些数值都假定部件放置在规定的测试夹具中,且电源施加在两个芯片中的一个上。

图25. 功率级额定电流

电源设计的最大额定电流通常由FET的Tjcn来规定。对于连续运行在150 C上的FET,通常由供应商来给出额定值。但因为电源板允许的工作温度和其它限制,客户经常选择较低的温度极限,比如105 C。他们的设计还将规定一个最高的环境温度,比如65 C。因此,FET的最大允许温升可能仅为40 C。如果设计中两个FET中的任一个达到了该极限,那么设计就会处于其最大工作电流上。

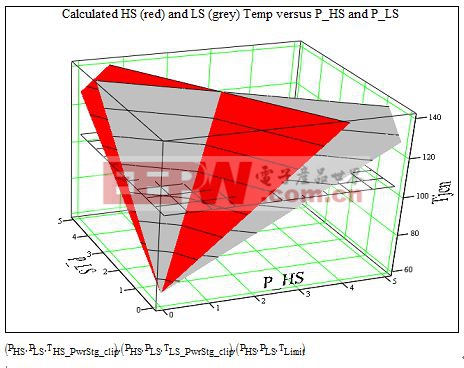

在图26的标绘中,对于每一个芯片,我们显示了Tjcn 105 C的设计极限如何与预测温度相交。设计极限将由Tjcn温度极限与两个平面的交叉点来设定。

注意,封装功率耗散极限转变为HS对LS功率变化比。相比于通过LS芯片面积输出1 W,通过HS芯片面积输出1 W产生的温升将会较大。

计算机辅助电路设计程序(PSPICE)和混合模式仿真等程序可以用于估算器件损耗[3]。然后可以使用热矩阵来预测每个FET的Tjcn。使用热矩阵来预测FET的Tjcn可提供几方面的了解。因为有两个发热元件且它们之间存在交叉耦合,该结构不再具有一个简单固定的Jcn-Amb阻抗指标。有效的封装热阻抗将是变化的,取决于HS和LS的功率比例。为预测每个芯片的最高温度,设计人员必须使用矩阵来计算Tjcn。

图26. HS和LS温度与功率对比

对于一系列HS / LS功率级,可以使用矩阵来计算FET对的最高Tjcn。而后,此数据可以转化为一组等高线,标绘出温度与功率的对比。图27显示了一个实例。典型的12 V -> 1.1 V电源设计将具有HS /LS功率分配,范围在30/70 到40/60内。如等高线显示,功率级设计的最大功率处理能力将随HS / LS功率损耗的比例变化而变化。针对章节II中引用的典型设计范围,已选择功率级HS和LS FET来提供优化的性能。

功率等高线还可用于判断散热封装设计的改进。图27显示的等高线可用于飞兆半导体的当代功率级部件与先前一代的对比。这两者的结构细节如图12所示。对于LS FET源极连接,先前一代部件使用粘接线。而当代部件使用固体金属夹。图27显示了通过此新设计实现的改进的热性能。在整个HS/LS功率范围内,新封装能够实现较高的净功率水平耗散。

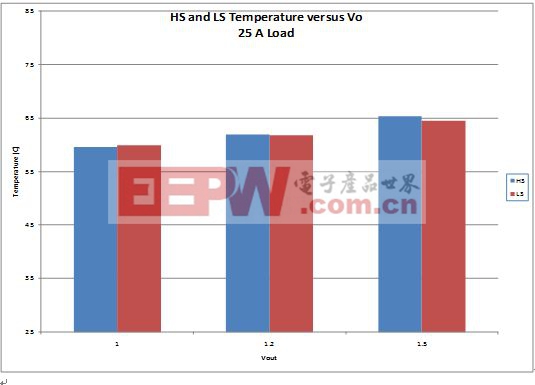

图27. 功率等高线

开关频率和电压比(Vout/Vin)等设计因素都将影响HS与LS功率损耗比。图28显示了测量数据,这里相同的功率级部件运行在几个不同的输出电压上。这两个芯片的温度由单个FET和来自相邻FET的热耦合这两者来确定。注意,在此实例中,随着Vo增加,最高温度从LS芯片转到HS芯片上。

图28. HS和LS测量温度与Vo的对比

IX.结论

在单一Power56封装中安装25A电源系统解决方案是一项挑战性任务。仅在几年前,25A解决方案需要三到四个FET。有了FET FOM、减少封装寄生和封装热性能方面的最新进展,25A功率级双芯片方案现已成为现实。

通过使用热矩阵分析,我们已经说明了在实际应用中如何比较封装的功率处理能力,以及最大功率和额定电流如何随HS / LS功率比例而变化。在一系列输出电压和工作频率下可应用该设计,这些知识是非常重要的。

评论