CMOS器件抗静电措施的研究

摘要:由于CMOS器件静电损伤90%是延迟失效,对整机应用的可靠性影响太大,因而有必要对CMOS器件进行抗静电措施。本文描述了CMOS器件受静电损伤的机理,从而对设计人员提出了几种在线路设计中如何抗静电,以保护CMOS器件不受损伤。

关键词:静电;静电损伤;CMOS器件;保护措施

静电是摩擦生电效应而产生的,所谓摩擦生电是在绝缘物表面做机械性的摩擦而产生过多的电子。因此静电可以在无意中产生,虽然总能量不大,但电势却很高,可达几万伏,有时超过十万伏。静电对人类既有利又有害,目前的静电复印技术,静电吸绒工艺等等都是利用静电作用,使静电造福人类;但静电会对电子元器件带来损伤,尤其是CMOS器件。美国有关专家统计了电子元器件特别是COMS器件受静电损伤而产生的巨大经济损失,每年高达50亿美元,对此美国集成电路生产厂家和使用单位高度重视防静电问题,美国还制定防静电的军用标准以及各种规范,连所有CMOS电路的详细规范中都有防静电的具体要求,目的就是为了提高器件和整机的应用可靠性。

国内对静电放电即高压静电场损伤CMOS及各种集成电路的严重性认识不足,导致很多CMOS器件受到损伤。要防止CMOS器件受到静电损伤,要从3个方面人手。首先在厂家生产过程中,通过设计以及生产工艺的保障使CMOS器件具有一定的抗静电能力,其次在运输移动过程中要提供相应的防静电措施,最后在使用过程中电路设计要采取抗静电措施。本文主要描述在使用过程中设计人员在线路设计中如何采取抗静电措施。

1 静电导致CMOS器件损伤的机理和结果

随着集成电路技术的发展,CMOS器件栅极氧化层的厚度越来越薄。早期CMOS器件工作频率较低,栅极氧化层厚度1 000~1 200 A,目前高速CMOS器件为提高效率,栅极氧化层只有600~700A左右,某些抗辐射的大规模电路,栅氧化厚度只有350~450A。CMOS栅极氧化层越薄,越容易受到静电的损伤而击穿栅极,导致CMOS器件失效,其失效机理有两种原因:

1)静电放电现象

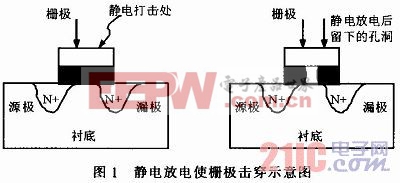

静电放电必须有带有静电的物体或人体触及到CMOS栅极的管脚,使CMOS栅极上积累电荷,如果CMOS栅极单位面积上聚集很高浓度的静电荷,使很薄的栅极上出现很高的电场,当电场达到一定水平,CMOS栅极就会击穿损坏,使这些静电荷通过击穿点泄放掉,这就是所谓静电放电。

2)高压静电场的静电感应现象

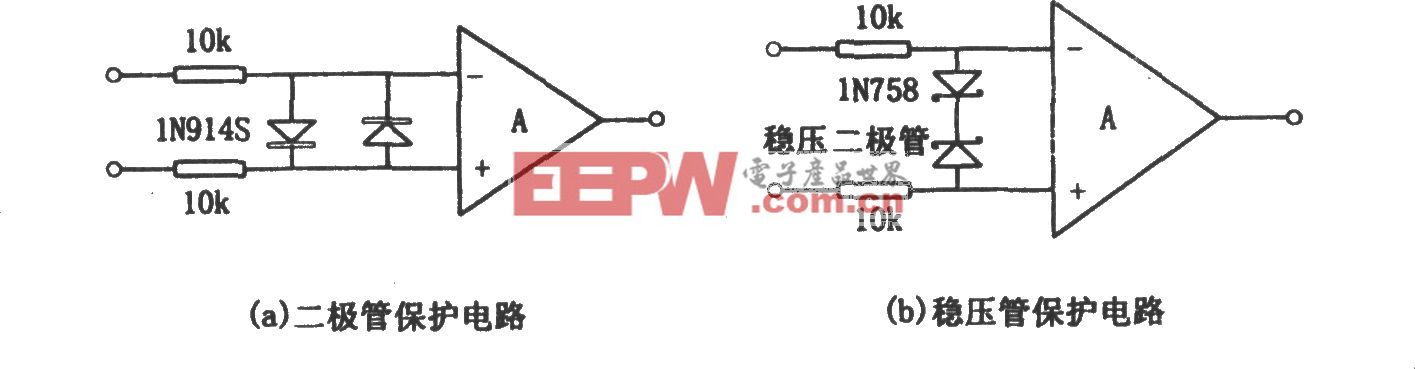

由于静电荷较多,静电电压较高,击穿时的放大电流较大,使CMOS栅极内部引线发热,有时热量足以烧融栅极的镀层或铝条。静电放电使栅极击穿如图1所示。

评论