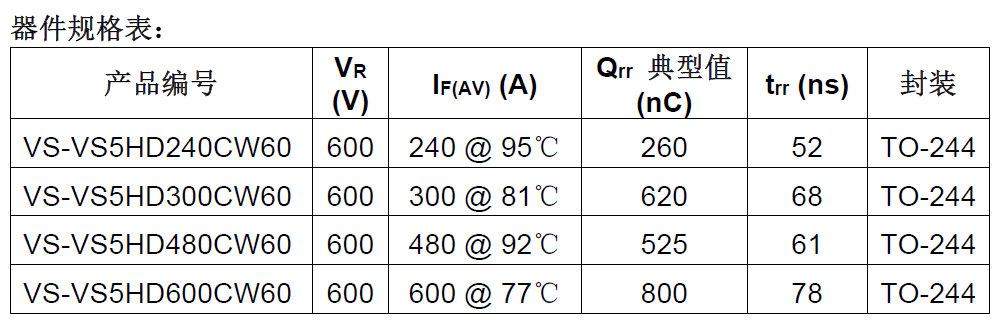

如何让同步整流器达到高效率标准

为了达到ClimateSaversCompuTIng及80PLUSPlatinum高效率标准,电源供应设计人员已经在电源系统中将相移全桥式DC/DC搭配使用同步整流器(FET)(图1)。对于这些高效率应用而言,相移全桥式转换器是绝佳的选择,因为DC/DC功率级的主要FET可达到零电压切换。同步输出整流器(QE及QF)的效率高于二极体整流,因此更容易达到这些高效率标准。然而,在无负载的条件下,这些同步整流器所耗用的电源,会高于输出的标准整流二极体。若要符合无负载条件下的待机输入电源需求,关闭同步整流器,并使用同步FET的本体二极体,进行输出整流更为适合。本文将介绍可根据转换器输入电源,开关相移全桥式转换器同步整流器的简易电路。

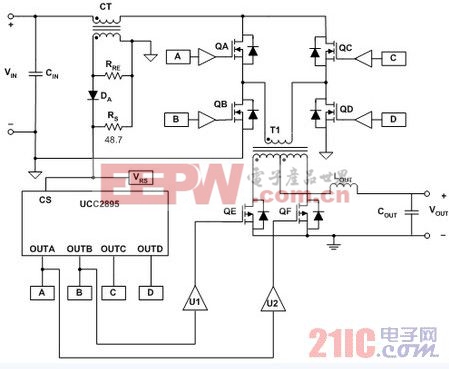

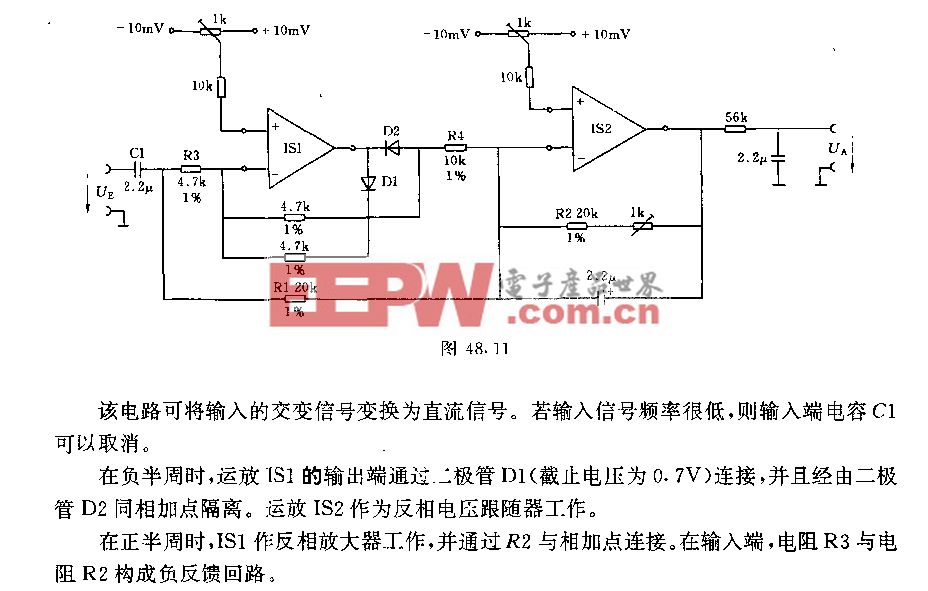

图1显示含同步整流器(QE及QF)的峰值电流模式,DC/DC相移全桥式转换器功能示意图。一般而言,FETQA至QF是以闸极驱动器/缓冲级加以驱动,QA至QD形成的H桥输入电流,则是以电流感应变压器(CT)网络加以测量。

图1.含同步整流器(QE及QF)的相移全桥式功能示意图。

如前所述,为达到零负载条件下的待机电源需求,关闭同步整流器为较适合的作法,因为驱动同步FET所耗用的电源,大于仅使用FET本体二极体进行标准整流所耗用的电源。在待机模式中,转换器的负载较轻,本体二极体耗用的电源相当少。以下等式可估算驱动一个同步整流器闸极所需的电源(PQEg)。在此等式中,变数QEg是FET闸极电量,Vg是FET最大闸极电压,变数fs是FET切换频率。在相移全桥式设计中,FETQE的闸极电量为115nC,并且以100kHz的12V闸极驱动信号加以驱动,因此大约需要138mW的电源驱动一个FET。在如此的条件下,驱动两个同步FET(QE及QF)所需的电源总计为276mW。如果同步整流器未关闭,驱动这些FET所需的电源,可能会补偿输入电源的25%至50%。额外的电源消耗会使设计不符合输入电源需求。

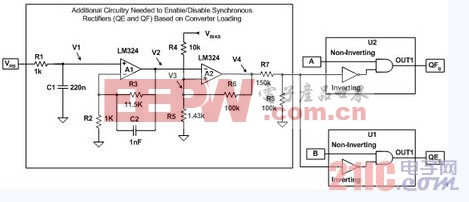

图2中显示的电路可新增至图1中显示的系统,根据系统负载控制启用及停用FETQE与QF的同步整流器。

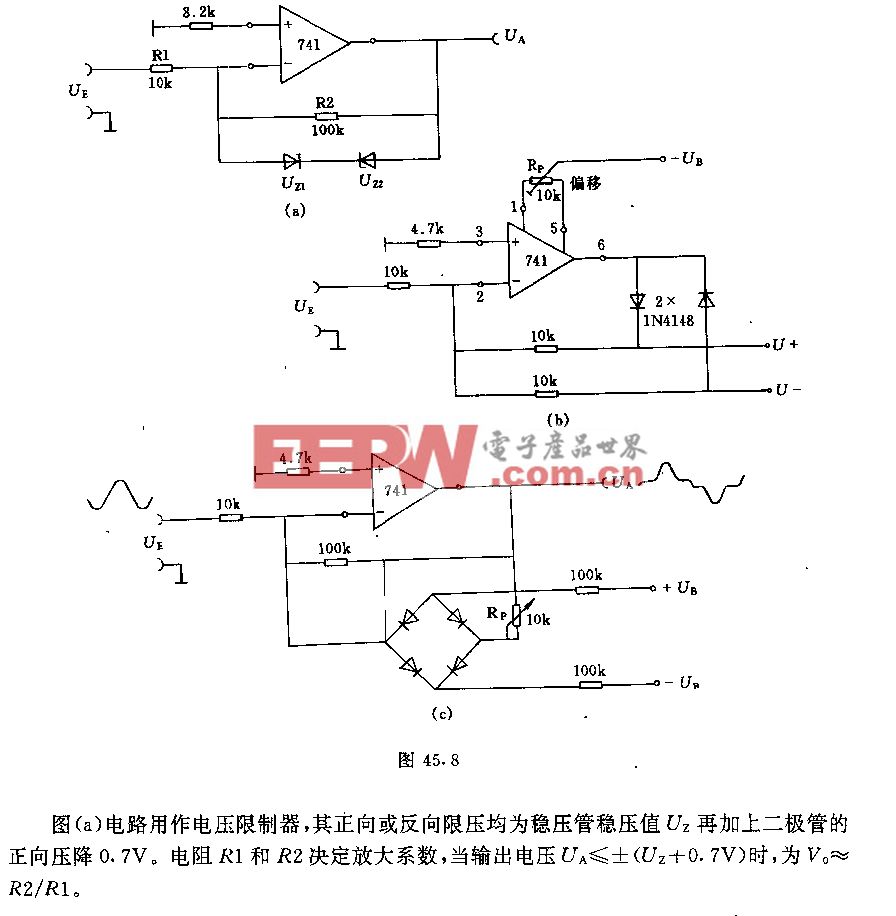

若要使此电路运作,需要同步闸极驱动器(U1及U2)产生反向及非反向输入。使用转换器电流感应电阻(VRS)的电流感应信号启用和停用FETQE及QF,此电路即可运作。电阻R1及C1会形成低频率电极为723Hz的低通滤波器,此滤波器所产生的DC电压(V1),可代表降压转换器电流感知电阻的平均电压大小。

在某些应用中,平均CS信号可低于0.25V,因此,电子元件A1、R3及R2的非反向放大器配置,可将平均电流感应信号(V1)放大为易于监控的可管理电流(V2)。放大器A2及电子元件R4、R5、R6会形成迟滞比较器,根据放大的平均电流感应信号,启用和停用同步整流器。电阻R7及R8即形成分压器,以减少放大器A2的输出,有助于防范闸极驱动器ICU1及U2过度输入电压。

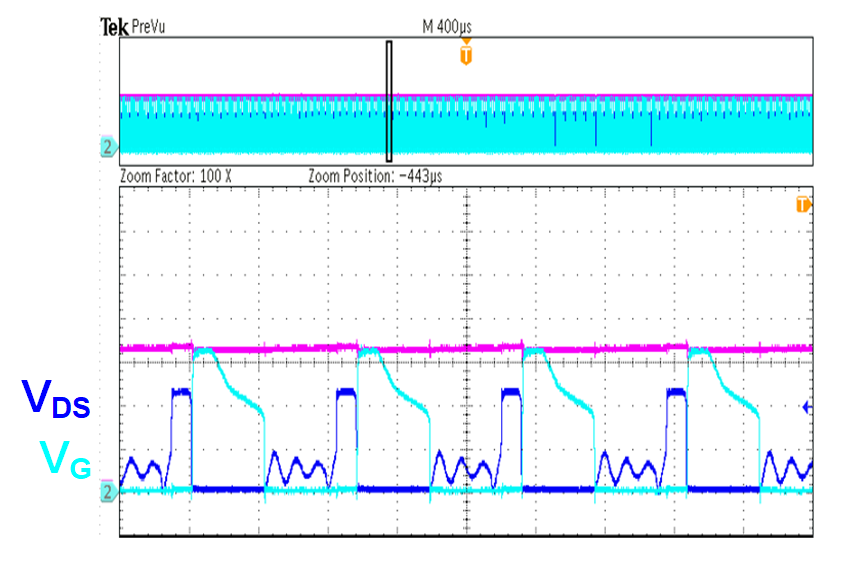

同步FET会根据迟滞比较器(V4)的输出予以启用及停用。比较器的输出升高时,闸极驱动器的输出会降低,以停止同步整流,并使用FET本体二极体进行标准整流。迟滞比较器输出(V4)降低时,相移全桥式转换器的闸极驱动信号A及B会控制FET闸极QE及QF,而且转换器会使用同步整流。

图2.关闭同步整流器的简单电路

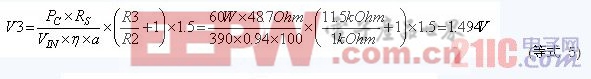

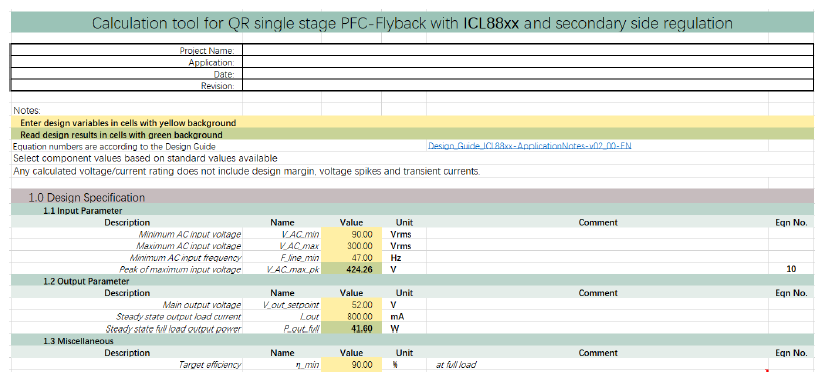

为说明如何设定此电路,可将此电路运用于如图1所示的600W相移全桥式转换器,其中的设计参数如下:

1.

输入电压

2.

最大输出功率

3.

输出电压

4.

峰间输出电感涟波电流

5.

电流感知变压器(CT)匝数比

低通滤波器相关文章:低通滤波器原理

评论