锂离子电池管理芯片的研究及其低功耗设计 ― 数模混合电路的低功耗设计方法(一)

2.1数字电路的低功耗设计

2.1.1数字电路的功耗模型和影响因素

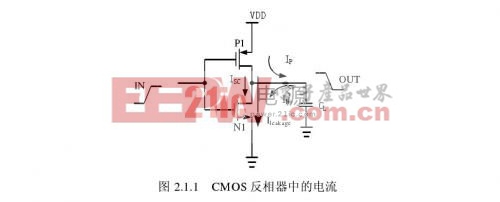

以图2.1.1所示的最基本的反相器单元为例,CMOS数字电路的功耗可以分为静态功耗和动态功耗两个部分:

其中,静态功耗

式中,第一项是P1和N1同时导通时的直流短路电流I SC引起的静态功耗;第二项是由漏泄电流引起,包括亚阈值电流和源漏区与衬底反向偏置时的漏泄电流。

动态功耗是对电路节点等效负载电容进行充放电所消耗的,也称为开关功耗,可表示为

式中,α0→1是开关活动因子,表示每个时钟周期内的状态跳变次数,其大小与电路结构、逻辑功能、输入信号的状态和节点的初始状态有关,一般地,CMOS电路中有α0→1≤1;CL是等效负载电容;ƒ是时钟频率;VDD是电源电压。

在0.18μm及其以上的CMOS电路功耗中,占主导地位的是动态功耗,有时还需要考虑短路功耗,而在一般情况下,漏泄电流和稳态偏置电流功耗都可以忽略。因此,要降低电路功耗,必然要从降低动态功耗入手,可以说,式(2.1.3)是低功耗数字电路的指导公式。

式(2.1.3)可以看出,降低电路的动态功耗,可以有以下四种途径:

第一,降低开关活动因子α0→1。在每个时钟周期内,并不是所有节点的状态都发生跳变,也不是所有状态的跳变都要消耗能量(如1→0的状态转变),所以降低开关活动因子的本质是,根据输入信号的组合状况,通过优化算法、逻辑结构等方法,减小不必要的耗能跳变。常采用的方法有,门控时钟技术、功耗估算/优化CAD技术和降低跳变编码技术。由于快速、准确地估算α0→1有很大的难度,所以急待开发实用的功耗估算CAD技术;其次,降低α0→1来降低动态功耗十分有效,并且有很大的潜力,所以这也是低功耗研究的重要方面之一。

第二,降低等效负载电容CL。CL主要由两方面构成:一方面是后续门的输入门电容和反相器源漏区的电容,它们和器件工艺有关;另一方面互连线电容。

因此要降低CL,可以采用优化逻辑电路(如减小所用晶体管数目)、优化晶体管尺寸、工艺映射中降低高活动因子的电容、版图中合理布局等方法。可以说,在设计的各个层次,都需要考虑到CL对功耗的影响。

第三,降低工作频率f.如果仅仅通过降低电路的频率来降低功耗,则它必然是以牺牲速度为代价的。所以时钟(频率)管理的策略是,在保证电路主频不变的情况下,通过多频率技术,即在不同系统部分中分配不同的频率,或者在设计版图时优化时钟树(Clock Tree),以尽可能地降低动态功耗。

第四,降低工作的电源电压V DD。由于功耗和电源电压的平方项成正比,所以这也是降低功耗最有效的方法。但在工艺尺寸确定、一级近似条件下,电路延迟与VDD满足下式

即有Td∝(CdVDD)/(VDD-VTH)2,其中W和L分别是器件的栅宽和栅长,μ为载流子迁移率,COX为氧化层电容,VTH为MOS管阈值电压。

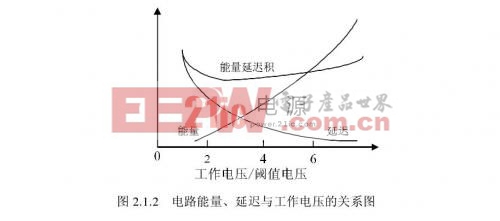

正如图2.1.2所示,从电路能量、延迟和工作电压的关系中可以看出,当VDD在2.5VTH到6VTH的范围内,延迟和能量延迟积的变化比较平缓,在VDD=3VTH时,这两者达到最低值。当工作电压继续下降到接近VTH时,延迟将急剧上升。

为了改善VDD下降引起的电路速度下降,可以采用并行或流水线结构,但这将使电路面积增大;另外一种补偿方法是,通过降低V TH来增大VDD /VTH值,但同时电路漏泄电流将增加,这时可以采用可变电压、可变阈值电压技术解决;在一些非关键电路中,也可以采用多电压、多阈值电压技术加以补偿。

2.1.2数字电路的低功耗设计方法

在目前ASIC设计过程中,常采用的是自顶向下(Top-Down)流程。对功耗的优化也就可以考虑到,在不同的设计层次,有目的地选择上述影响功耗的因素,在给定的性能约束下,实现功耗最小化的目标。

从抽象层次来分,低功耗设计可以分为:系统级、结构级/算法级、寄存器传输级、逻辑/门级和版图级。在设计的不同层次,影响功耗的因素所起的作用各不相同,因此功耗优化的效果也不同;综合地看,在芯片设计时越早考虑低功耗,取得的效果也越显著。

1系统、结构级

在这个层次上,从系统功能出发,分为静态低功耗设计和动态功耗管理(Dynamic Power Management,DPM)技术两种。静态低功耗设计是在考虑系统的具体实现时,采用不同的电路结构和不同的编码方式,在设计阶段(如综合和编辑)实现低功耗;而动态功耗管理技术是和运行期间的行为密切相关,它需要充分考虑系统和任务或者和负载的关系,做出相应的判决,来实现低功耗。

1)静态低功耗方法

①电路结构

并行(Parallelism)结构是将一个数据处理功能模块分为几个相同的子模块,并行处理数据,然后选择对应的输出。这种方案允许在保持总模块速度不变的情况下,降低各个子模块的电压、频率等因素,使总功耗降低,但代价是将增加芯片的面积。

流水线(Pipeline)结构是在保持总体速度不变的前提下,将数据分段后连续慢速处理,速度余量则可以通过降低电压来降低功耗。如果和并行结构相结合,就可以取得更好的功耗节省效果。

②电压技术

和改进电路结构一样,电压技术也是为了补偿工作电压的降低带来的速度下降[26,27]。多电压技术,是针对不同的性能要求,系统中各部分也采用不同的工作电压以节省功耗,但这需要额外的片内电压转换器。

③编码优化

常用的二进制编码中,采用所有空闲的高位作符号扩展位,这将增加耗能的跳变。符号-数值编码(如格雷码等)方法只用最高位代表符号,如果用它来代替二进制编码,可以减少由于数据符号改变而产生的功耗。

2)动态功耗管理技术

是系统级功耗优化中的一个有效手段。根据负载的请求,子系统可以分为工作和空闲模式。在空闲模式下,可以将子系统关断,进入低功耗的待机(Standby)

和不消耗能量的睡眠(Sleep)状态;反之,则将子系统唤醒,进入正常的工作模式。

评论