电能计量芯片Sigma-Delta ADC降采样滤波器设计(二)

3 补偿滤波器的设计

本文引用地址:http://www.amcfsurvey.com/article/174622.htm从图3 可以看出,CIC 滤波器幅频特性曲线在通带内并不平坦,在通带内信号被衰减.为了克服这一缺点,可加入补偿滤波器,它的幅频特性正好与CIC 滤波器相反,完成对频率响应的补偿,从而扩展了系统的频率特性.

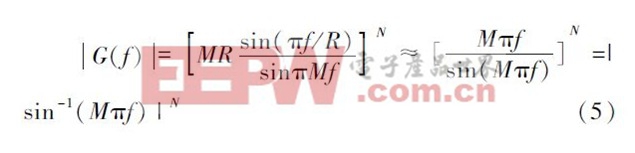

补偿的基本原理是使通带内信号的衰减为零.补偿滤波器的幅值响应与(4)式相反。

当R 足够大时,补偿滤波器的响应接近反SINC 函数,因此补偿滤波器也称之为反SINC 滤波器.

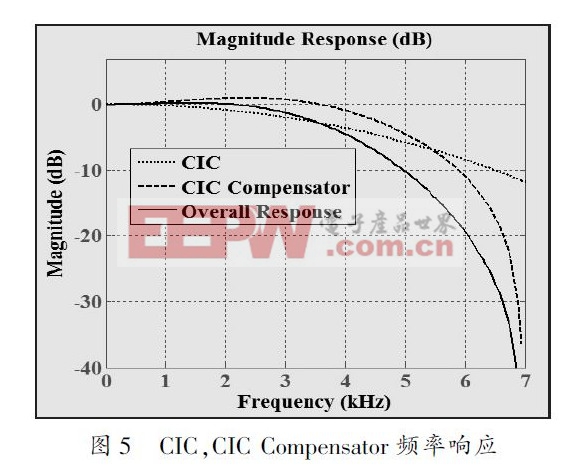

补偿滤波器一般可借助MATLAB 仿真,再与CIC滤波器级联观察补偿后总的频率响应是否满足系统要求,从而得出补偿滤波器的参数.图5 为图3 中CIC滤波器加入补偿后的幅频特性曲线图.

在图3 中,衰减点在1kHz 左右,而从图5 中可以看出,加入补偿滤波器后,衰减点出现在2. 5kHz 左右,因此,补偿滤波器可以很好地克服由于CIC 滤波器在通带内幅值衰减的问题.

补偿滤波器的采样频率为CIC 滤波器降采样后的频率( FS / R),为了避免频率混叠,其截止频率的最大值为采样频率的一半:FC = (FS / R) / 2.在实际应用中,为了得到更加理想的频率特性,截止频率一般设定为采样频率的四分之一,即FC = (FS / R ) /4.

4 实验数据以及结论

本设计针对电能计量芯片.Sigma-Delta 的采样频率为1792kHz,数字电路工作时钟为14kHz.CIC 滤波器的降采样率R =64.根据经验,当CIC 滤波器的阶数比Sigma-Delta 调制器的阶数高一阶时可以达到较好的效果,因此,本CIC 滤波器设定为3 阶,延迟因子为1.半带滤波器采样频率为28kHz,通过MATLAB仿真,6 阶通带频率为2. 5kHz 可以满足系统要求.在实验过程中利用Verilog HDL 语言,HBF 采样对称结构以及CSD 编码,在CSMC 0. 18μm 工艺下综合,得到面积与功耗如表1 所示.

5 结束语

本设计根据电能计量芯片的要求,对Sigma-Delta降采样滤波器进行优化设计.由于单级CIC 滤波器在实现高倍降采样率时功耗大,效果不理想,因此,本设计对128 倍的降采样进行分级抽取,前级采用CIC 滤波器进行64 倍抽取,后级采用半带滤波器实现2 倍抽取.在HBF 的实现过程中采用对称结构以及CSD 编码,减少运算过程中乘法的次数以及乘法运算过程中移位相加次数,降低了电路功耗.与传统方法相比,经优化后,电路面积减少8% ,功耗降低15% .

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

数字滤波器相关文章:数字滤波器原理

评论