TMS320F240片内PWM实现D/A扩展功能

关键词:数字信号处理器 TMS320F240 PWM D/A转换

TMS320F240(简称F240) 作为一种高速、高集成度、低成本的微控制器,功能非常强大。美中不足的是,F240芯片本身虽然集成了众多满足数字控制系统所需的先进外围设备,包括A/D转换等功能,却唯独没有集成D/A转换功能,因此,在TMS320F240芯片的实际应用过程中,为其增加 D/A转换接口是很有必要的。

本文提出的基于F240芯片PWM输出的D/A转换扩展功能设计,是一种对F240片内的D/A转换设计。通过F240片内的PWM输出,再加上简单的外围电路及对应的软件设计,实现对PWM的信号处理,得到稳定、精确的模拟量输出。

1 原理及误差分析

1.1 基本原理

F240芯片提供的PWM输出,是一种周期和占空比均可变、幅值为5 V的脉宽调制信号。实现PWM信号到D/A转换输出的理想方法是:采用模拟低通滤波器滤掉PWM输出的高频部分,保留低频的直流分量,即可得到对应的D/A输出,如(图1)所示。低通滤波器的带宽决定了D/A输出的带宽范围。

为了对PWM信号的频谱进行分析,以下提供了一个设计滤波器的理论基础。傅里叶变换理论告诉我们,任何一个周期为T的连续信号f(t),都可以表达为频率是基频的整数倍的正、余弦谐波分量之和。它是以时间轴原点为对称点的、单极性的PWM信号,表达式为

其中,f=1/T为基频,式中An、 Bn为各自独立的傅里叶系数:

由于f(t)是一个关于原点对称的偶函数,因此Bn项为0,只需计算An项即可。只要扣除直流分量A0,由f(t)=-f(t+T/2),An的偶系数也将为0,因此,对占空比为k、幅值为5 V的PWM信号有:

A0=5k

Bn=0

由式(5)可知,直流分量A0就是所需要的 D/A输出,只要改变PWM信号的占空比k,就能得到电压范围为0~5 V的D/A转换输出;An代表PWM信号的高频直流分量,频率为PWM信号基频的整数倍。因此,对于基频为10 kHz的PWM信号,一个理想的剪切频率≤10 kHz的滤波器即可完全滤掉PWM信号的高频谐波分量An,得到低频的直流分量A0,从而实现PWM信号到D/A输出的转换。

1.2 误差分析

D/A转换输出的电压信号有一个纹波叠加在直流分量上。这是D/A转换误差的来源之一。影响D/A转换误差的另外一个重要因素,取决于PWM信号的基频。对于时钟频率为20 MHz的F240芯片,产生一个20 kHz的PWM信号,意味着每产生一个周期的PWM信号,要计数1000个时钟。即所得的直流分量的最小输出为1个时钟产生的PWM信号,等于5 mV(5 V1/1000),刚好小于10位的D/A转换器的最小输出4.8 mV(5 V/1024)。因此,理想情况下,PWM信号的频率越低,所得的直流分量就越小,D/A转换的分辨率也就相应的越高。如果将PWM信号的频率从20 kHz降到10 kHz,则直流分量输出的最小输出为2.5 mV(5 V/2000),接近于11位的分辨率。但是,随着PWM信号基频的减小,谐波分量的频率也随之降低,就会有更多的谐波通过相同带宽的低通滤波器,造成输出的直流分量的纹波更大,导致D/A转换的分辨率降低。所以,单纯降低PWM信号的频率不能获得较高的分辨率。通过以上分析可知,基于DSP芯片PWM输出的D/A转换输出的误差,取决于通过低通滤波器的高频分量所产生的纹波和由PWM信号的频率决定的最小输出电压这两个方面。所以要获得最佳的D/A分辨率,在选取PWM信号的频率时不能太小,要适当地折衷,选取一个最合适的值。如表1所列,通过Matlab仿真,可以得到最佳D/A分辨率下的PWM信号频率。

表1 不同设计参数下F240芯片PWM输出实现D/A转换的分辨率

| 低通滤波器阶数 | 传递函数 | -3dB带宽/Hz | PWM频率f/kHz | 纹波Vpp/V | PWM频率决定的分辨率 | D/A转换的分辨率/位 |

| 一阶 | 1/(RCs+1) | 1000 | 10 | 0.78 | 2.5 | 2.7 |

| 20 | 0.39 | 5.0 | 3.7 | |||

| 二阶 | ω2n/(s2+2ξωns+ω2n) | 1000 | 10 | 0.062 | 2.5 | 6.3 |

| 20 | 0.016 | 5.0 | 7.9 | |||

| 三阶 | 1/(a3s3+a2s2+a1s+a0) | 1000 | 10 | 0.0064 | 2.5 | 9.1 |

| 20 | 0.00081 | 5.0 | 9.7 |

2 硬件设计

一般来说,F240的PWM输出要通过具有一阶阻容滤波及光电隔离功能的I/O接口板后,方可与实际控制对象连接。为了获得高精度的D/A输出,在滤波之前应先通过缓冲器,整体设计框图如图2所示。

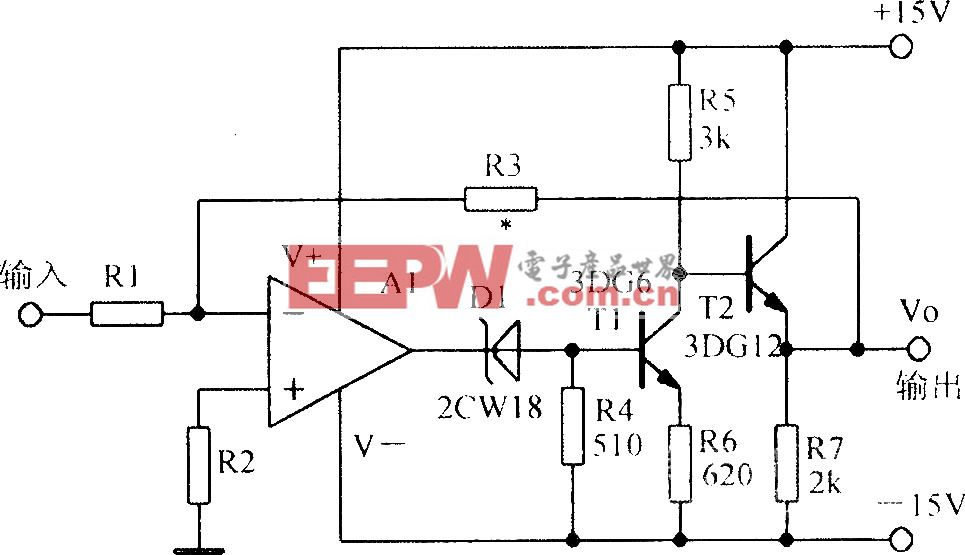

滤波器的运算放大器选用OP07。它温漂小、阻抗低、吸收电流大、精度高。考虑到实际情况,设计模拟低通滤波器的阶数一般不超过三阶,否则会增大系统的复杂性,增加系统的成本。下面主要介绍有源低通滤波器的参数设计。

2.1 二阶Butterworth低通滤波器

图3(a)所示,是二阶Butterworth低通滤波器(最平幅值滤波器)的一种实现电路,其传递函数为

在-3 dB带宽为1000 kHz的条件下:

A0=1

由于考虑到不可能找到与所计算的R、C值完全一致的电阻、电容值,而只能选取与实际的电阻、电容值最接近的值,故求解得到:

C1 = 0.1 μF, C2=0.01 μF,

R1=22 kΩ, R2=1 kΩ (7)

在这些参数下,实际的带宽是1074 Hz,Q值为0.645,与理想的二阶Butterworth低通滤波器有一定的误差。

2.2 三阶低通滤波器

图3(b)所示为三阶低通滤波器的一种实现电路,其传递函数为

Vo/Vi=1/(a3s3+a2s2+a1s+a0) (8)

其中, a0=1+R1/R4

a1=R1(C1+C2)+(R2+R3)C2+R1C2(R2+R3)/R4

a2=R3C2C3(R1+R2)+R2R3C2C3+R1R2R3C2C3/R4

a3=R1R2R3C1C2C3

在-3 dB带宽为1000 kHz的条件下,求解得到:

R1=1.6 kΩ,R2=2.4 kΩ,R3=7.5 kΩ,R4=∞,C1=0.1μF,C2=0.01μF,C3=0.047μF (9)

R4决定滤波器直流分量的增益,选取R4=∞(即不安装R4),则D/A输出增益为1;要想改变带宽大小,只须保持R4和电容值不变,改变其它电阻的阻值即可。

图3 低通滤波器电路

3 软件程序设计和实验结果

利用TMS320F240配套的EVM(Evaluation Module)板作为DSP的实验平台,给定一模拟电压作为F240的A/D输入,将A/D转换的值作为产生PWM波形的DSP定时器中比较寄存器的值;通过中断,不断获取最新的A/D转换值,改变PWM波形的占空比,得到对应幅值的PWM波形,再将所得的20 kHz的PWM信号输入给滤波器,用数字示波器观察滤波器的D/A输出,以评价这种D/A转换方法的实际效果。

3.1 通过D/A转换产生对应幅值PWM波形的DSP程序

基于DSP功能模块化的特点,其汇编程序的编制主要分三个步骤:① 初始化设置时钟源模块,得到所需的CPUCLK和SYSCLK; ② 设置事件管理模块,初始化定时器和A/D转换操作; ③ 编写定时中断服务子程序,即可完成从A/D转换产生对应幅值的PWM波形输出。部分程序代码如下:

;设置 PLL模块

LDP #224;

SPLK #0000000001000001b,CKCR0

;SYSCLK=CPUCLK/2

SPLK #0000000010111011b,CKCR1

;CLKIN(OSC)=10MHz, CPUCLK=20MHz

SPLK #0000000011000011b,CKCR0

;使能锁相环(PLL)操作

SPLK #0100000011000000b,SYSCR

;CLKOUT=CPUCLK

;设置EV 管理器

LDP #232;

SPLK #0,T1CMPR ;初始化定时比较寄存器

SPLK #0000000001010101b,GPTCON

;通用定时器的PWM输出为低有效

SPLK #1000,T1PR ;设置PWM波形的周期为20 kHz

SPLK #0000h,T1CNT ;初始化计数寄存器

SPLK #0001000000001010b,T1CON

;设置连续增计数方式,使能比较操作

SPLK #0000000010000000b,EVIMRA

;清除定时器1比较中断屏蔽位

LDP #224

SPLK #1000110100000010b,ADCTRL1

;设置A/D连续转换模式,选择通道CH0

SPLK #0000000000000101b,ADCTRL2

;设置A/D转换输入时钟预定标因子为16

LDP #232

SBIT1 T1CON,B6_MSK ;使能定时器1中断启动位

LDP #224

SBIT1 ADCTRL1,B0_MSK;使能A/D转换启动位

CLRC INTM;

END B END ;等待定时器1中断的产生

;产生PWM 波形ISR

Change_CMPR:

LDP #224 ;定时器1比较中断服务子程序

LACC ADCTRL1;

SACL ADCTRL1 ;清除片内A/D转换中断标志位

LACC ADCFIFO1;读取最新的A/D转换值

RPT #5;

SFR ;把存于结果寄存器的高10位的A/D

;转换值移至ACC的低十位

LDP #232;

SACL T1CMPR ;将A/D转换值存于定时比较寄存器

LACC EVIFRA;

SACL EVIFRA ; 清除定时器中断标志

CLRC INTM ;开中断

RET ;中断返回

3.2 PWM输出实现D/A转换功能的实验结果

如图4所示,是在给定一恒定的3.5 V模拟电压作为F240的A/D输入的情况下,所得的PWM输出实现D/A转换的波形图。

波形1为不通过低通滤波器的原始PWM信号。

波形2为PWM信号通过一阶低通模拟低通滤波器后的D/A输出波形,滤波器参数为R=1 kΩ,C=0.1μF,带宽为1592 Hz。可以看出,一阶下的D/A输出为一锯齿波,可用性很差。

波形3为PWM信号通过二阶Butterworth低通模拟滤波器后的D/A输出波形,滤波器参数按照式(7)选取。可以看出,二阶下的D/A输出平均值接近3.5 V,只是尖峰毛刺比较大,有一定的可用性。

波形4为PWM信号通过三阶低通模拟滤波器后的D/A输出波形,滤波器参数按照式(9)选取。可以看出,三阶下的D/A输出毛刺很小,D/A转换的分辨率约为9.2位, 非常接近于理想的D/A输出,可用性强。

实验结果表明,DSP的PWM信号经过三阶低通模拟滤波器后,得到的D/A转换输出带宽较大,在1000 Hz左右;分辨率较高,约为9.5位,可以满足实际应用的需要。

pwm相关文章:pwm原理

评论