用TMS320LF2407和FPGA实现电能质量监测

随着人们对电能质量要求的日益提高,如何保证电能质量就成为一个热门话题。电能质量监测的一项主要内容是谐波检测,即对多路模拟信号进行采集并进行谐波分析。本系统对16路50Hz模块信号进行采样并进行64次谐波分析。如果仅仅依靠一个MCU(单片机或控制型DSP)来进行处理,往往达不到实时性要求,所以采用DSP和FPGA相结合的方法。利用DSP对电力参数进行计算,利用FPGA进行谐波分析。

系统主要包括数据采集电路、ADC模块、FPGA模块、DSP模块及上位机显示模块,其结构如图1所示。

图1 系统框图

1 数据采集电路和ADC模块

对经过互感器调理成-3.3~+3.3V(ADC测量的最大量程)的信号进行采样。根据香农抽样定理,对最高频率fc的连续信号进行抽样,须保留其全部内容。抽样频率fs满足条件为:fs≥2fc。如图1系统框图所示,本系统中,ADC采用的是MAX125,其单通道的转换时间为3μs。若利用内部的采样保持器,可以同时采样4路信号,转换时间为12μs。为了同时采集已经过调理的16路模拟信号,必须对其进行采样/保持。在前向通道使用16路采样/保持器(SMP04),再使用多路开关(MAX306)依次选择这16路信号,输入到MAX125的一个通道(CH1A),并由FPGA发出转换信号CONVST。待转换结束,MAX125发出INT中断,通知FPGA读取转换结果。总之,由FPGA中的ADC控制模块完成对MAX125、MAX306及SMP04的控制以及对MAX125信号的中断响应。

2 FPGA模块

FPGA模块主要完成通信、数据采集、ADC模块的数据读取、保存及底层的信号预处理计算――谐波分析。FPGA工作流程如图2所示。其子模块有:ADC控制模块、ADC采样数据保存区、FFT工作RAM、FFT运算结果保存区、开方修改正表、开方运算单元、谐波系数存放区以及串行、并行通信控制模块。

图2 FPGA工作流程图

(1)ADC控制模块

图3所示ADC控制模块除了完成对MAX125、MAX306及SMP04的控制外,还要响应MAX125的中断(INT)来读取转换结果,并将其保存到ADC采样数据保存区。如图3所示,为了更准确地产生控制时序,对系统的采样周期及相位的锁定都采取了相应的处理。待采样信号先经过方波转换电路,将其转换成0~+3.3V的方波信号,再经过FPGA中的数字锁相环模块,根据外部时钟和计数器测量出其周期,作为下一个待采样信号的采样周期。这样就减小了由于待采样信号频率的漂移而带来的采样周期的误差。本系统采用的数字锁相环在FPGA中实现,其具体的性能为:锁相环的捕捉带Δfmax=12.5Hz,锁相频率为50Hz12.5Hz=37.5~62.5Hz,随后产生的采样周期Ts能够满足实际应用的要求。同时,根据多路开关信号和计数器,产生ADC采样数据保存区地址,保存来自MAX125的14位数字量。

(2)谐波分析模块

本系统中,采用快速傅里叶变换(FFT)进行谐波分析,主要因为FFT使N点DFT的乘法计算由N2次减少到(N/2)log2N次。由FFT工作流程图可知,本系统在分析64次谐波时,整个运算分6级。在第一级蝶形运算中,蝶形运算单元根据算法控制模块的控制信号,从ADC采样数据保存区取出原始数据,从旋转因子ROM中取出旋转因子,进行FFT的第一级蝶形运算,并将结果存入FFT工作RAM。在以后的各级蝶形运算中,蝶形运算单元从FFT工作RAM中取出间数据,从旋转因子ROM中取出旋转因子,进行运算,直至第六级蝶形运算结束,并将结果存放到运算结果保存区,以便进行各次谐波系数计算。

在FFT运算中,一个蝶形运算单元和一组工作RAM被重复使用,其中最重要的是FFT工作控制逻辑的实现。它主要完成从ADC采样数据保存区取出数据、向FFT工作RAM中写入和读取数据以及向FFT结果存放区存放结果等工作。

根据FFT运算的结果z=dinr+jdini,计算各次谐波的系数(其中,dinr为结果的实路,dini为结果的虚部,。在进行开方运算时,若设计64M13位长度的存储器进行查表计算,对于现有的可编程逻辑器件来说是很难实现的。因此,本次设计中采用了修正查表算法:将待开方的数据z=(dinr2+dini2)左移m次(m为偶数),直到其最高两位不全为0,此时z变为z1;取z1的高8位来查表(此时表长为2 8=256个字)得到t1;使用牛顿一次迭代公式t=(t1+z1/t1)/2,对t1进行修正得到t;最后将t右移m/2次,得到开方结果。实验证明,上述修正后的查表法误差在允许的范围内,对本系统来说是可行的。

在软件方面,为了提高芯片的性能及资源利用率,采用Quartus II 2.0t Synplify7.1。在Synplify中使用有效的代码,采取流水线设计、优化组合逻辑及减少逻辑延时等措施来提高整体性能,还进行了多个文件的分块设计,然后将这些文件映射到顶层文件进行综合,并运行VHDL或者Verilog HDL对单个文件编写、信真和优化。在用到组合逻辑时,Synplify会尽量避免锁存器的出现,节省逻辑单元。对于ACEX系列的芯片,它还支持寄存器配平技术、流水线操作、复制逻辑模块及使用LPM函数等技术来提高其整体性能。Synplify和其它结合软件一样,编译后生成的电子设计交换格式文件(EDIF)可以在MAX+PLUS II或Quartus II 2.0中进行编译、分别引脚和其它优化处理。因此,采用Quartus II 2.0和Synplify7.1相结合,对FPGA进行设计、优化及综合,不仅能提高系统性能,还能提高芯片资源的利用率。

(3)通信接口模块

为了灵活地与外界系统进行连接,FPGA提供了并行通信和串行通信两种形式。并行通信可以直接和DSP连接组成电力监测和控制系统;串行通信不仅可以方便地和DSP连接,不可以和不具备谐波分析功能的系统组成更加完善的电力监测系统。

以于并行通信,如系统框图所示,根据规划好的LF2407扩展I/O空间,由LF2407的高位地址线的逻辑组合来产生FPGA选片信号,低位地址线向LF2407输出要访问数据的地址,在IS引脚的下降沿,FPGA中的数据传输到LF2407的数据总线。值得注意的是,在编写FPGA的并行通信模块时,除了编写相应的控制程序以外,还要利用LF2407的IS引脚来选通FPGA的三态总线进行数据输出,这样可以避免FPGA与LF2407的数据接口影响LF2407的工作。

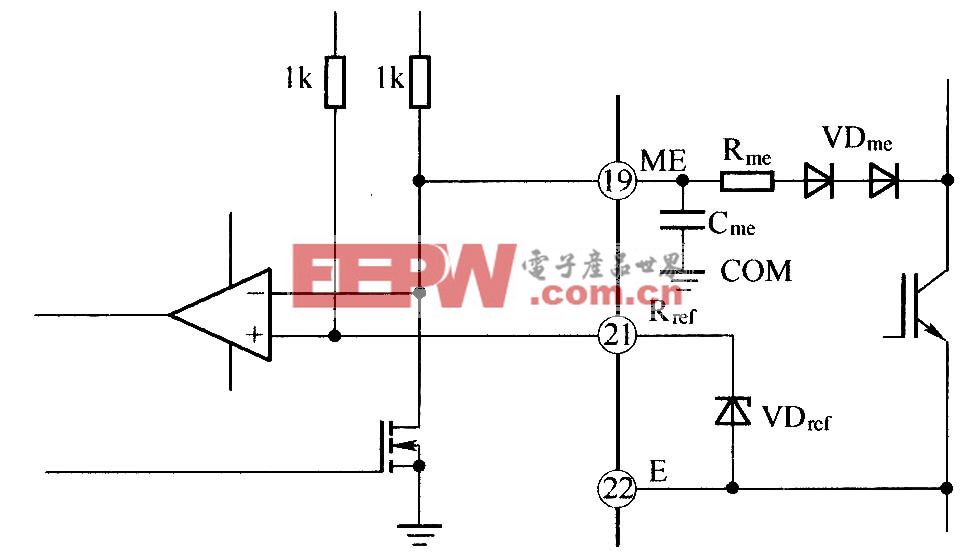

如果利用FPGA进行串行通信,则可以完善已有的电力监测系统。为了使其能和现有的设备更好的进行连接,还设计了TMS320LF2407和FPGA之间的串行通信。本系统中,LF2407包含了可以直接利用RS232通信的串行通信接口(SCI)模块,所以对FPGA编写串行通信接口模块时,要保证和LF2407相同的通信格式。本系统在实际设计中采用的通信格式为:1个起始位,8个数据位,1个奇/校验位,1个停止位。TMS320LF2407的串口通讯电路如图5所示。

FPGA的UART模块中,确定相同通信格式的同时,还要确定相同的波特率,并根据波特率产生发送、接收时钟。对于数据的发送,FPGA监测txrdy(发送就绪)信号。如果txrdy=“1”,就从待发送数据区中取出数据写入UART的数据总线,随后产生一位起始位。然后,利用发送时钟触发移位寄存器,将待发送数据送到内部寄存器,将数据依次送到发送端(TX)。最后,根据发送数据的“1”的个数,加上校验位和停止位,就实现了数据的串行发送。

FPGA的监测单元监测到RX的下降沿,则启动接收单元。在采样时钟的上升沿对接收信号进行采样,高电平为“1”,低电平为“0”。然后通过移位寄存器,将串行数据转换成并行的8位数据,完成数据的接收。

图5 串口通信电路图

3 DSP模块

根据算法的分配,高层的信号处理量小,但控制结构复杂,适合用处理速度较快的DSP来处理。本系统中,DSP主要是根据FPGA中模拟量的采样结果和运算结果,计算电力参数以及发出相应的控制信号。如有必要,还可以用液晶来显示结果。

对于LF2407和FPGA的并行通信,使用LF2407的扩展I/O来读取FPGA中ADC采样数据保存区和各次谐波系数放区中数据。LF2407可以直接使用IN和OUT指令对FPGA进行读写。

对于串行通信,LF2407向FPGA发送数据。只要查询SCICTL2的7号位,来判断发送器是否为高。如果为空,LF2407就可以向FPGA发送数据(命令),控制FPGA的运行。同样,LF2407采用中断方式接收从FPGA发送来的数据。LF2407接收中断的向量地址为INT1(0002H),外围中断向量为0006H。

4 总结

本系统已完成实验室样机制作与调试,证明设计正确,可以完成对电力质量进行监测的任务。在电力监测系统中,通过FPGA和DSP相结合,可使测量更灵活、控制更方便。本系统有选择地进行并行通信或串行通信,使设计更加灵活多变,有利于系统的扩展,方便与其它电力测控系统直接相边,而且适于模块化设计,提高算法效率,缩短开发周期。

评论