Motorola32位嵌入式微处理器MPC860的开发应用

MPC860 PowerQUICC是当今比较流行、性能相当优越的单片集成嵌入式微处理器。它内部集成了微处理器和一些控制领域的常用外围组件,特别适用于互联网络和数据通信。PowerQUICC可以称为MC68360在网络和数据通信领域的新一代产品,各方面性能包括适应性、扩展能力和集成度等获得了较大提高。MPC860 PowerQUICC通信处理器可根据用户不同的要求提供2~4个串行通信控制器、不同规格的指令和数据缓存,各种级别的网络协议支持。该产品专为宽带接入设备如路由器、接入集线器、LAN/WAN交换机、PBX系统和STM网关等设计。

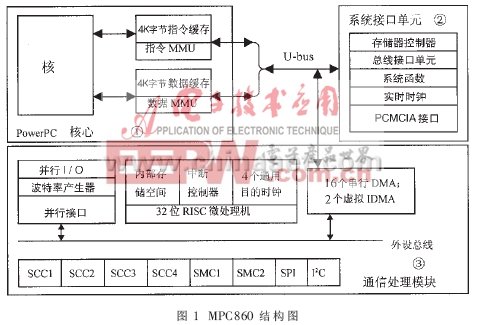

图1是MPC860结构图。它包括三个主要模块:PowerPC核心、系统接口单元(SIU)、通信处理模块(CPM)。

PowerPC是主要的处理机单元,通常称为 Embedded PowerPC核心(或EPPC)。它包括数据和指令的缓存和存储器管理单元(MMU),在40MHz时钟时为50 MIPS 指令速度。

第二个主要的模块为系统接口单元(SIU)。主要包括:总线监视器、假中断监视器、软件看门狗、中断定时器和实时时钟(RTC)、复位控制器、不占用内部开销的片内总线仲裁、JTAG1149.1测试口。它的一个主要功能是提供内部总线和外部总线的接口。

第三个主要模块为通信处理机模块(CPM)。主要包括:RISC控制器、所有串行通道口支持连续接收和发送模式、5K字节双口RAM、16个串行DMA(SDMA)通道、三个平行I/O寄存器、四个波特率独立的发生器(可以连接到任意一个SCC和SMC,并允许运行中改变,支持自动波特率)、四个串行通信控制器(SCC)(支持以太网、HDLC/SDLC、HDLC 总线)、两个串行管理控制器(SMC)(UART方式或透明传输)、一个串行外围接口电路(SPI)(MC68302 SCP的扩展,支持主从模式,支持同一总线上多主操作)、一个I2C(Inter-Integrated Circuit)接口(支持主从模式,支持多主环境)。CPM在几个不同的通信设备如SCC和SMC上发送、接收数据,所有的通信设备可以独立工作。SCC和SMC也可以用于时分复用总线。

在图1中,CPM模块中有一个32位RISC微处理机。MPC860有两个CPU:PowerPC和32位RISC。PowerPC执行高层代码,RISC处理实际通信的低层通信功能。由于CPM分担了嵌入式PowerPC核的外围工作任务,这种双处理器体系结构功耗要低于传统体系结构的处理器。两个处理器主要是通过内部存储空间相互配合工作。在存储器区,每个处理器都可以设置控制位、读状态位。在图1中,有16个串行DMA单元。每个通信设备都有一个发送DMA和接收DMA,32位RISC控制这16个串行DMA在通信设备和存储器之间传送数据。当MPC860接收数据时,串行DMA从通信设备接收数据并放入存储器中;发送数据顺序相反,串行DMA从存储器中取数据,送到通信设备,串行DMA只服务CPM的RISC,但是两个虚拟IDMA可以为用户DMA所用。

2 ADM系统

2.1 系统概述

ADM即分插复用器,它是一个三端口设备,具有两个SDH光接口(线性接口),通过另一端可以灵活地上/下路复用在STM信号中的低速率信号。ADM内部还具有时隙交换功能,允许两个STM信号之间不同VC的互联,并能方便地进行带宽管理。在实际网络中,根据ADM的结构特点,可灵活地用在网络中不同的位置。在本系统中,主要任务是将155.52Mb/s的STM-1高速信号经光/电转换,从帧结构恢复出低速的2.048Mb/s的E1信号,其逆过程正好相反。从理论上来说,将STM-1信号可以上下63路E1信号,为了系统的可维护性和美观性,故采用4块支路,每块上下16路。

从图2可以看出,分插复用器ADM是一种新型的网络单元,是SDH中应用最广、最富特色的设备。它将同步复用和数字交叉连接功能综合于一体,具有灵活的分插任意支路信号的能力,在网络设计上有很大的灵活性;采用同步复用方式和灵活的复用映射结构,可使高速信号一次直接分插出低速支路信号,即所谓的一步复用特性。ADM利用时隙交换实现宽带管理,并且无需分接和终结整体信号,即可将各种G.703规定的接口信号(PDH)或STM-1信号(SDH)接入STM-M(M>1)内作任何支路。

群路:对接收信号进行光/电转换,再生恢复出接收数据,同时将高速的信号转变为并行的信号,从中分离出接收段开销SOH,并对指针进行解释,提取VC-4POH,进入虚容器VC-4处理,恢复下行的VC-4净负荷,同时提供FPGA(交叉叠加模块)接口;反过来将需要上行的VC-4净负荷插入VC-4通道开销POH,经过AU-4指针调整,并插入段开销SOH,经电/光转化上线路,成为STM-1信号。

支路:可用专用的芯片从数据总线具有VC-4的信号经过均衡、码型恢复,解复用出所需的63路E1信号;反过来,将E1信号异步映射进入TU-12中,并将格式定为VC-4。

交叉叠加矩阵模块:特定用途集成电路(FPGA)提供了良好的解决方案,降低了产生电信号的复杂性;另外,也有利于降低不同特征的结合。所有通信都经过此模块,不管是低速向高速复用,还是高速向低速分插,甚至高速流的通过。此连接将有固定通道或者有程序设定,配置为分插复用设备、终端及转发器。在该模块中,信号进行相应的延迟,产生一定的片选和触发信号,特别对于复用的信号,有直接的触发作用。

时钟板:在数字传输和素质交换的数字网络中,网同步特别重要。网同步的目标就是使各节点时钟频率和相位都控制在预先确定的容差范围内,以便使网内的数字流实现正确有效的传输和交换,避免数据因时钟不同步而产生滑动损伤。时钟板的功能就是实现网同步,为SDH单元提供系统时钟信号。

公务板:利用STM再生段中的E1字节来实现SDH网中各站之间的语音联络。本系统公务板的特点为:

(1)PCM语音编码,64Kbit/s编码速率,音质较好;

(2)能实现点对点、一点对多点、点对组、点对全线的呼叫;

(3)多方会议通话方式;

(4)联络信令插在PCM通话数据流中,对通话质量无影响。

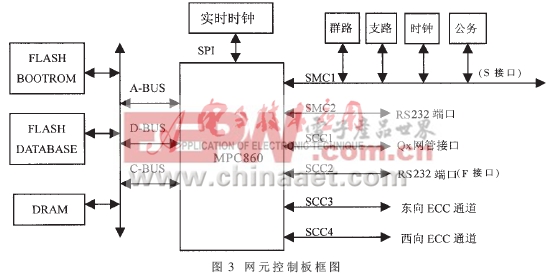

2.2 系统控制器――网元控制板

对于每一个单模块的控制管理,采用最普遍的80C31单片机,管理通信及监测系统性能,对不同的告警及时上报或屏蔽。主控制器采用实时处理很强和通信能力高的Motorola32位单片集成微处理器MPC860,采用串口RS232与各模块中的单片机进行多机(8031)通信,及时处理告警及环路能力,此外还提供了高级网管的Qx接口。网管系统可通过一个Qx接口或内嵌的通信通道(ECC)对所有网络内的同步复接器进行中央控制,如图3所示。时钟分配为:提供同步时钟基准信号,用于内部的数据总线及外部的接口。此处用三级振荡器(4.6ppm的误差),给不同模块提供不同的时钟。

在网元控制板中,配置了FLASH BOOTROM嵌入式VxWorks实时多任务操作系统的引导程序,用于保存重要的数据;FLASH DATABASE存储应用程序;DRAM作为程序运行和保存临时文件的空间。

在这个网元控制板中,MPC860是核心单元,它实现对各通信口的处理和调度,满足实时处理的要求。

Qx接口:Qx接口用于与上层网管通信,采用以太网(Ethernet)接口,使用CPU(MPC860)的SCC1。为得到以太网的标准电平,需要用以太网接口芯片扩展出以太网的标准TP接口,用专门的变压器芯片转换电平。一般的网管用PC机,加上相应的网管软件就可以对各单板进行管理和性能监测,比较形象直观地反映系统情况。

linux操作系统文章专题:linux操作系统详解(linux不再难懂) 隔离器相关文章:隔离器原理

评论