基于ZLG500的智能卡门禁系统设计

1 读写模块ZLG500简介

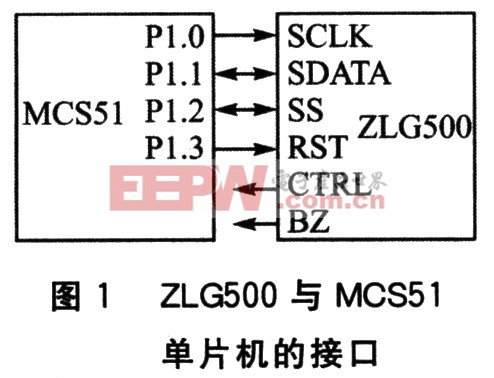

1.1 ZLG500与MCU的接口原理

ZLG500模块采用Philips公司最新的高集成ISO14443读卡芯片MF RC500,它能读写RC500内EEPROM,提供三线制SPI接口,并具有控制线输出端口,能与任何MCU连接。ZLG500与MCS51单片机的接口原理图如图1所示。此外该模块的EMC性能优良,并且自带无源蜂鸣器信号输出,能用软件控制其输出频率及输出持续时间。

图中SCLK、SDATA、SS为ZLG500与MCU相连接的控制线,分别为时钟线、数据线和片选。主控制器的MCU和读卡模块内的MCU通过此三线相连。接口空闲时,主机的SS=1,SCLK=O,SDATA=0,而从机的SS=1,SCLK=1,SDATA=O。其中SS和DATA都是双向的,而时钟线SCLK是单向的,即时钟只能由主控制器产生,该信号必须严格遵守时序规范,否则将出现通信错误,此时读卡模块必须释放该线。

SS还作为数据发送使能端。若一方有数据要发送给另一方,则该方控制SS线为低电平,并在发送结束后将该线置高电平。接收数据方不得控制该线,双方必须遵守通信协议,不得同时控制该线。SDATA为数据线,由数据发送端控制数据,接收端必须释放该线。该线在一次传输开始时还同时作为数据接收端的响应信号。

1.2 ZLG500与MCU接口的时序及通信协议

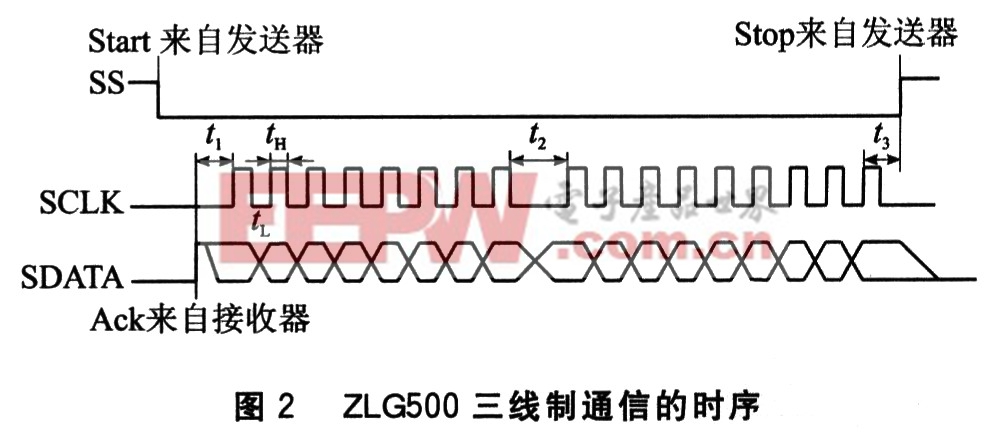

ZLG500与MCU无论数据传输的方向如何,SPI线上信号的波形总是如图2所示。由图中可以看出,在SS为低时,时钟和数据线上的信号才有效;在SCLK为低时SDATA变化,在SCLK为高时SDATA应保持稳定。

以上传输中,从数据发送器请求开始至数据接收器响应的时间是不确定的,取决于接收器内的MCU是否忙,因此有必要设置看门狗定时器对数据接收器的响应进行监视。一旦接收器响应,则MCU必须根据数据传输方向,严格控制以下几个时间,以确保数据传输无误。

t1:数据接收器响应至MCU产生第一个SCLK上升沿的时间。

t2:2个字节传输之间SCLK低电平的持续时间。

t3:传输最后1个字节的最后1位的SCLK信号的上升沿至SS上升沿的时间。

tH:SCLK信号的高电平持续时间。

tL:SCLK信号的低电平持续时间。

在数据传输方向不同时,对时间t1、t2、t3、tH和tL都有不同的要求。

MCU与ZLG500的通信必须先由MCU发送命令和数据给ZLG500,ZLG500执行命令完毕后,将命令执行的状态和响应数据发回MCU。

开始通信前,收发双方必须处于空闲状态。首先由MCU发出SS下降沿信号,然后等待ZLG500在SDATA线上的响应,若在50 ms内未检测到此信号,则退出本次传输。若正确响应,则MCU可将命令和数据发送出去。

然后MCU等待ZLG500发回的状态和响应数据,即等待SS线上的下降沿信号。若在50 ms内未检测到此信号,则退出本次传输;若正确检测到SS信号,则可以接收状态和数据。

2 智能卡门禁系统设计

2.1 总体结构

系统采用Philips公司的非接触智能IC卡Mifare 1(M1)卡。以M1卡作为用户卡,以其全球唯一的序列号SN为依据控制门的开启。由于它是一个高频卡,工作频率为13.5 MHz,因而具有较强的抗干扰能力且读写距离远(2.5~10 cm)。

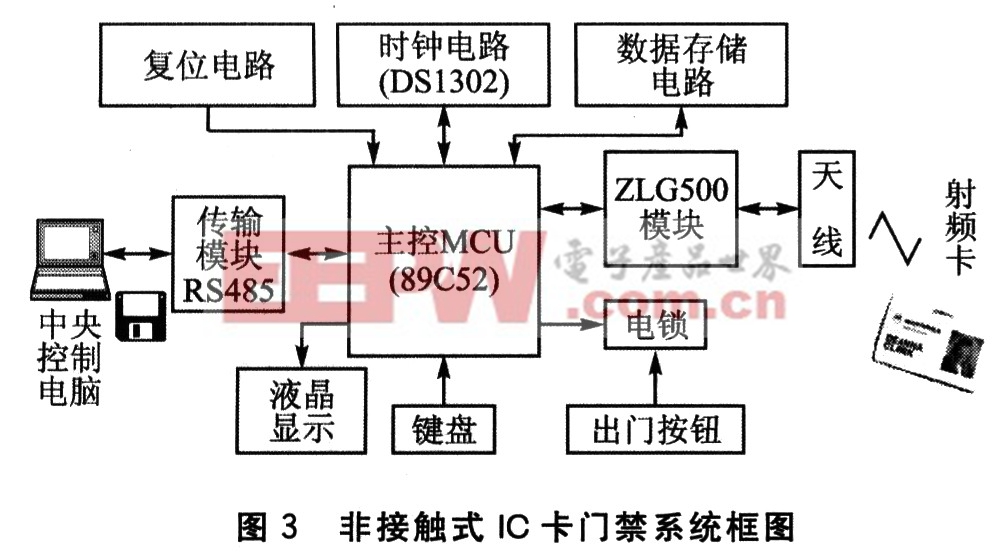

整个智能卡门禁系统分为三大部分:其一是读写器部分,包括MCU、复位电路、时钟电路、显示电路、键盘、数据存储等主控模块及非接触IC卡读写模块和电锁驱动部分;其二是中央控制电脑的软件管理系统模块;其三是中央控制电脑与读写器之间的数据传输模块。总体系统框图如图3所示。

评论