并行模数转换器ADS8364与TMS320F2812的接口设计

0 引言

本文引用地址:http://www.amcfsurvey.com/article/173825.htmADS8364是美国德州仪器公司(TI)的一款六通道、16位并行输出、同步采样的模数转换器。该芯片提供了一个灵活的高速并行接口,可以直接与数字信号处理器TMS320F2812相连。本文主要介绍了这个接口的软、硬件设计,着重论述了这两款芯片是如何配置启动和工作的。本设计广泛应用于电机控制、多轴定位系统、三相功率转换、多通道数据采集等场合。

1 芯片简介

ADS8364是一款六路模拟输入、16位并行输出的模数转换器。六路模拟输入分为三组(A,B 和C) ,每个输入端都有一个保持信号来实现所有通道的同时采样与转换功能,非常适合于多路(多种)采集系统的需要。ADS8364提供了一个灵活的高速并行接口,可以运行在直接寻址、循环采样、FIFO等三种模式,每个通道的输出数据都可直接作为一个16bit的字。

TMS320F2812是TI公司生产的一款DSP芯片,TMS320F28X系列是当今世界上最先进的32位定点DSP芯片。它不但运行速度高,处理功能强大,并且具有丰富的片内外围设备,便于接口和模块化设计。它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、智能化仪器仪表及电机伺服控制系统等。

2 ADS8364的工作原理

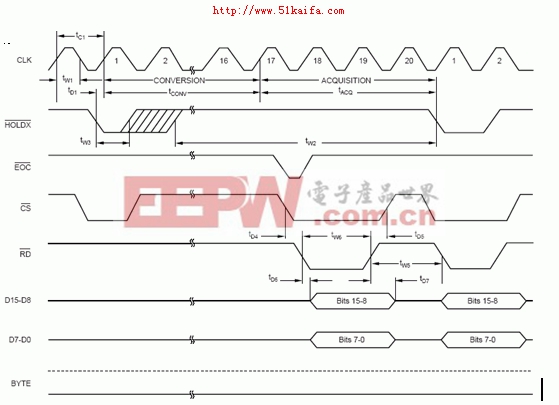

ADS8364的最大工作频率可达5MHz,采样/转换可在20个转换时钟周期内完成。ADS8364的六个通道可以同时进行采样/转换。吞吐率最大可达250ksps。ADS8364采用+5V工作电压,并带有80DB共模抑制的全差分输入通道以及六个4μs连续近似的模数转换器、六个差分采样放大器。另外,在REFIN和REFOUT引脚内部还带有+2.5V参考电压。ADS8364的差分输入可在-VREF到+VREF之间变化。三个保持信号(HOLDA、HOLDB、HOLDC)可以启动指定通道的转换。当三个保持信号同时被选通时,其转换结果将保存在六个寄存器中。对于每一个读操作,ADS8364均输出十六位数据,地址/模式信号(A0,A1,A2)可以选择如何从ADS8364读取数据,也可以选择单通道、单周期或FIFO模式。在ADS8364的HOLDX保持至少20ns的低电平时,转换开始。这个低电平可使各个通道的采样保持放大器同时处于保持状态从而使每个通道同时开始转换。当转换结果被存入输出寄存器后,引脚EOC的输出将保持半个时钟周期的低电平。另外,通过置RD和CS为低电平可使数据读出到并行输出总线。

ADS8364工作时序图

电路部分主要分为DSP芯片的最小系统设计和ADS8364的接口设计。分别给予介绍。

3.1 TMS320F2812的最小系统设计:

(1)电源和复位部分:本设计采用外部5V直流电压供电。通过DC/DC器件产生3.3V的内核电压VDD和1.8V的I/O电压VDDIO电压。电源芯片TPS767D318为双电源输出,一路为3.3V、一路为1.8V。每路电源的最大输出电流为1A。芯片还提供两个宽度为200ms的低电平复位脉冲。本设计的复位信号分两种:上电复位、手动复位。上电复位由芯片TPS767D318产生,手动复位由电阻电容组成的电路产生。

评论